# POLITECNICO DI TORINO

# Facoltà di Ingegneria dell'Informazione Corso di Laurea in Ingegneria Elettronica

# Tesi di Laurea

# Progetto e Realizzazione del Satellite PICPOT: Scheda di Acquisizione Immagini

Relatori: ing. Claudio Passerone prof. Leonardo M. Reyneri

> Candidato: Mauro Caule

# **Indice**

#### **Sommario**

#### 1. Introduzione

- 1.1 Il progetto PICPOT

- 1.2 Vincoli ambiente spaziale

- 1.2.1 Single event upset

- 1.2.2 Single event latchup

## 2. Progetto Hardware

- 2.1 Specifiche scheda Payload

- 2.2 Scelta dei componenti

- 2.2.1 Criteri di scelta dei componenti

- 2.2.2 Componenti Video

- 2.2.3 Processore

- 2.2.4 Memorie

- 2.3 Funzionamento componenti principali

- 2.3.1 DSP Blackfin BF-532

- 2.3.2 Decoder Video TVP5150AP

- 2.3.2.1 ITU-R BT.656-4

- 2.3.2.2 Programmazione via I<sup>2</sup>C

- 2.3.3 Videocamere

- 2.3.4 Memoria FLASH

- 2.3.5 Memoria SRAM

- 2.3.6 Memoria SDRAM

- 2.4 Interfacce

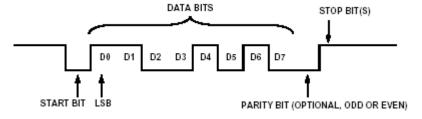

- 2.4.1 UART

- 2.4.2 SPI

- 2.4.3 JTAG/IEEE 1149.1

- 2.4.4 Alimentazioni

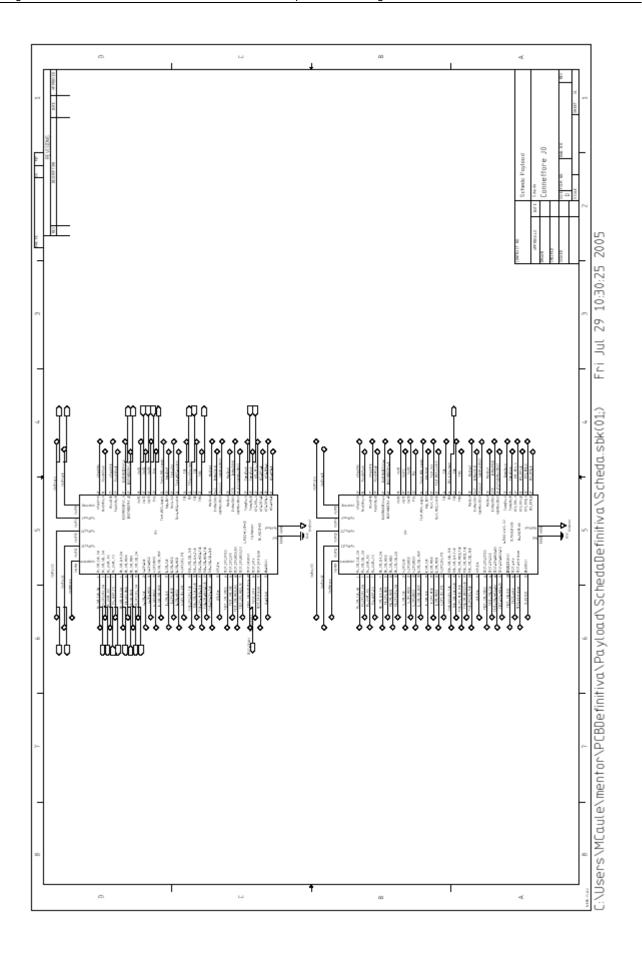

- 2.4.5 Connettore J0

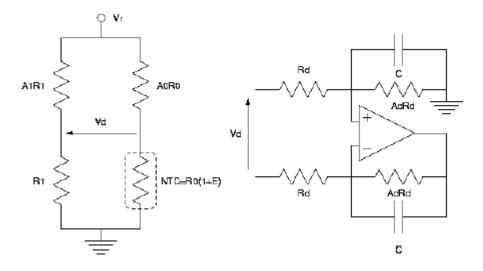

- 2.5 Sensore di Temperatura

- 2.6 Consumi energetici

#### 3. Realizzazione

- 3.1 Libreria

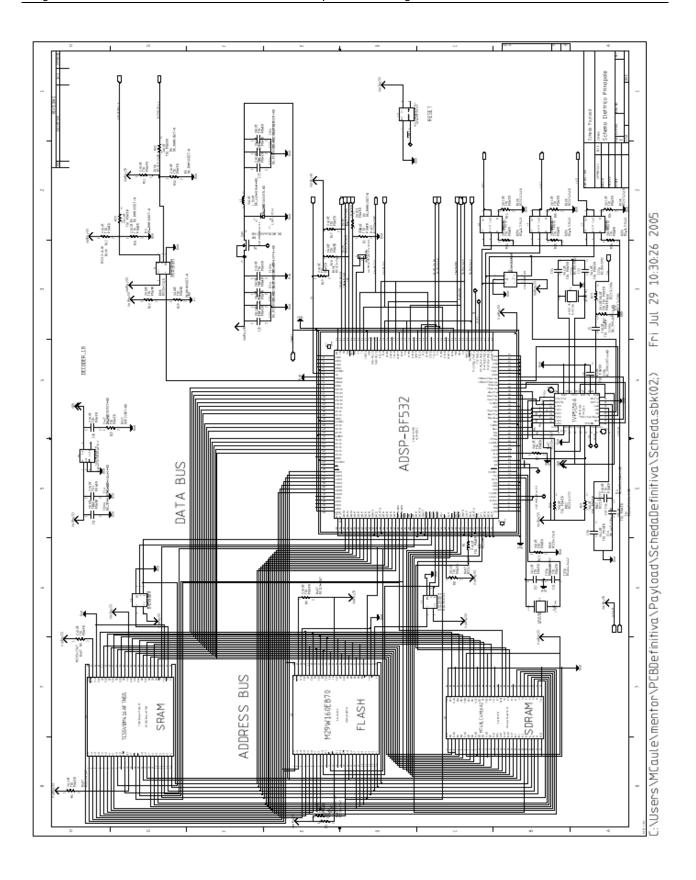

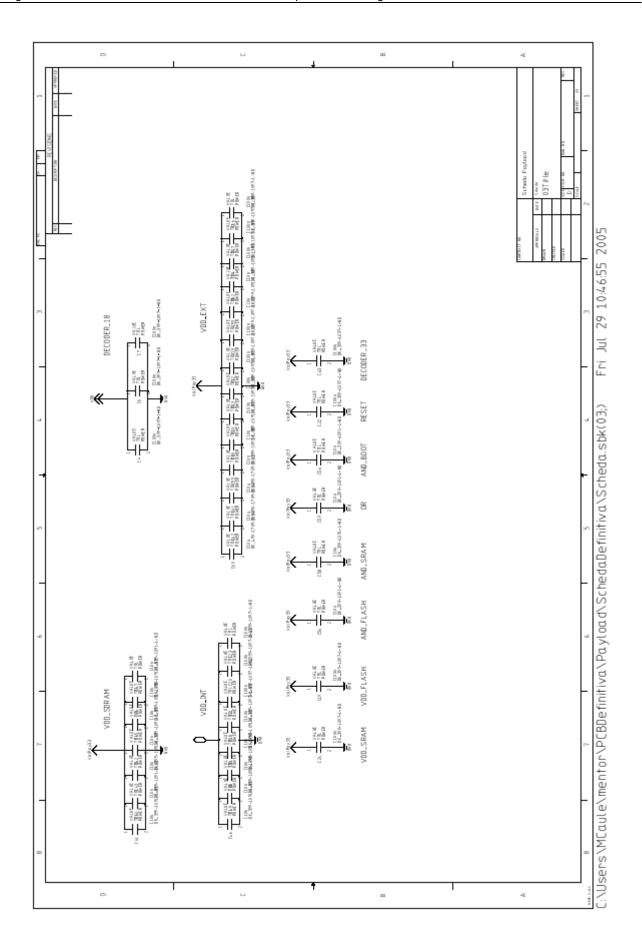

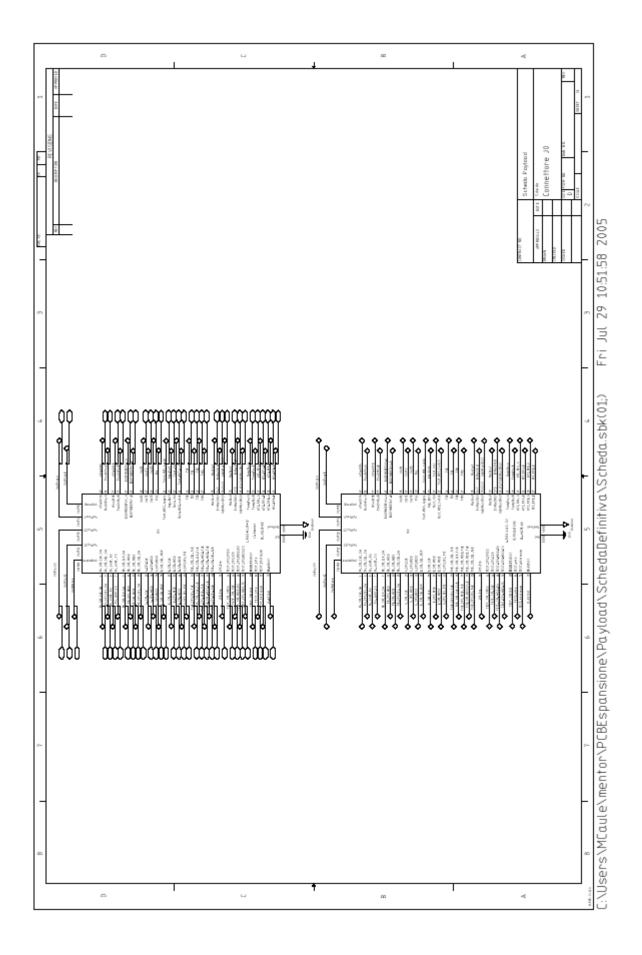

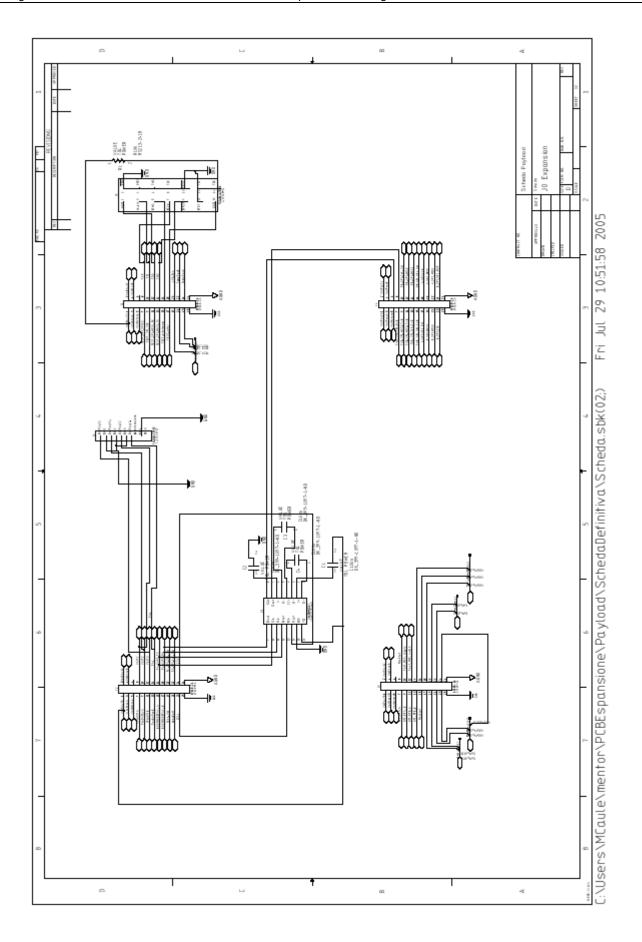

- 3.2 Schema Elettrico

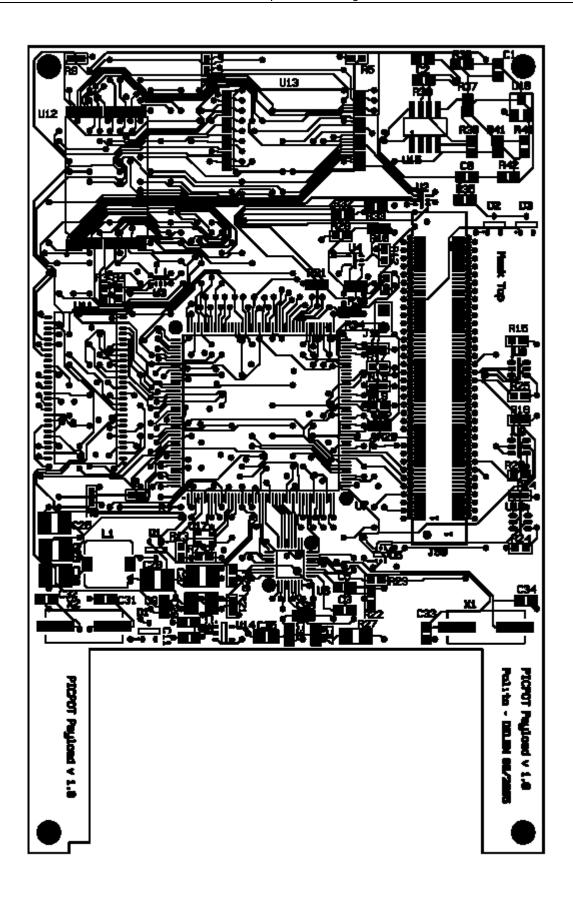

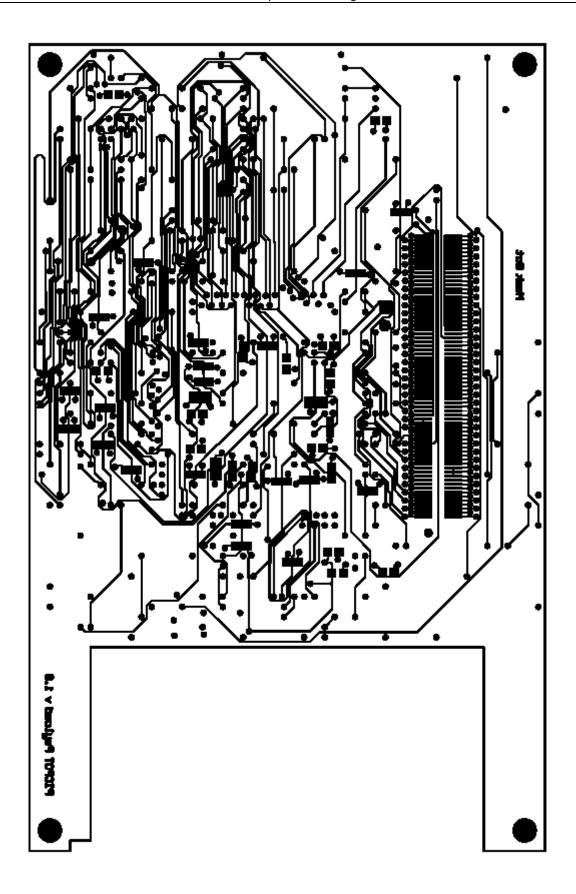

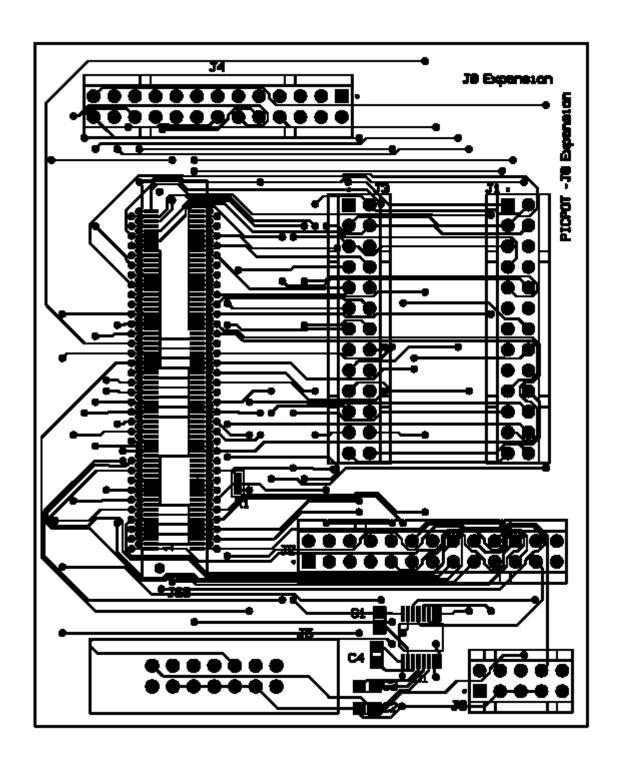

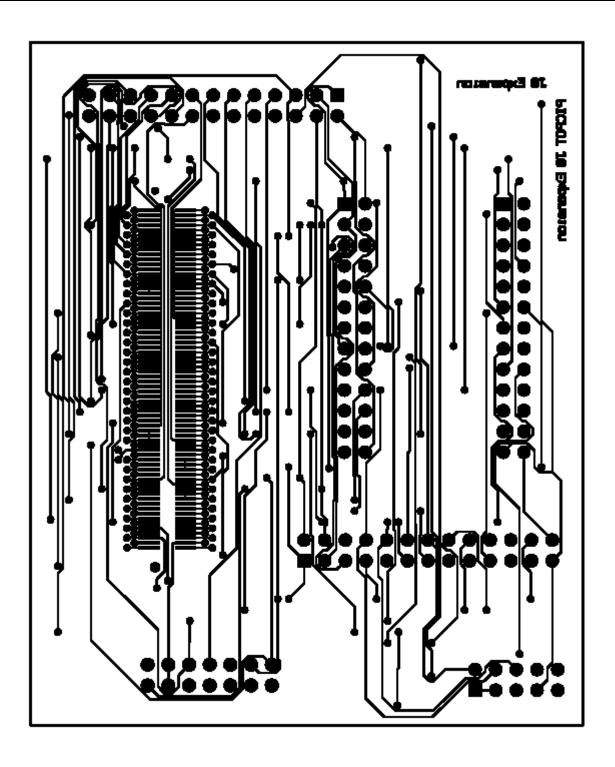

- 3.3 PCB

- 3.3.1 Vincoli strutturali

- 3.3.2 Disposizione dei componenti

- 3.3.3 Routing

- 3.4 Saldatura

- 3.5 Scheda espansione J0

### 4. Progetto Software

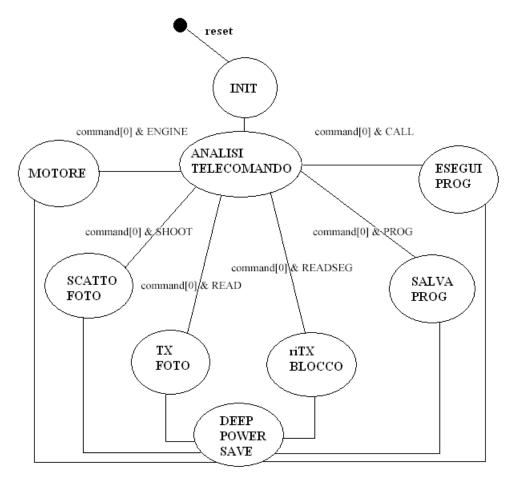

- 4.1 Diagramma a stati

- 4.2 Descrizione generale

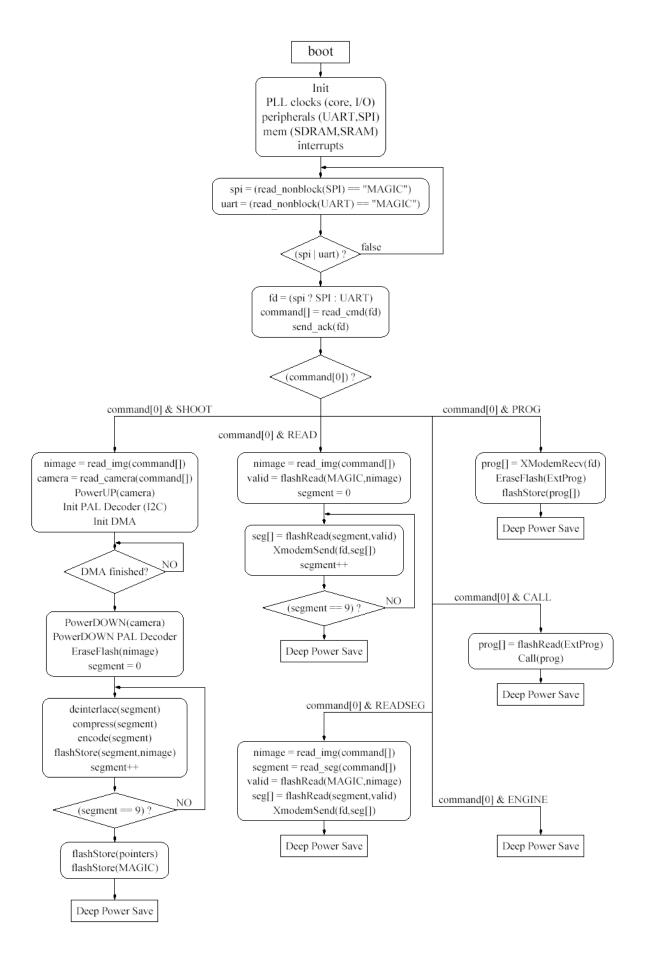

- 4.2.1 Scatto Foto

- 4.2.2 Trasmissione Foto

- 4.2.3 Ritrasmissione Blocco

- 4.2.4 Salvataggio Programma Utente

- 4.2.5 Esecuzione Programma Utente

- 4.2.6 Motore

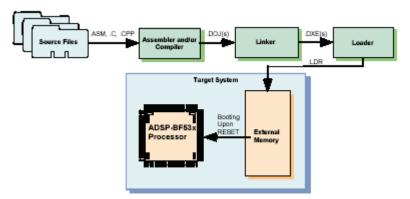

- 4.3 Flusso di sviluppo del software

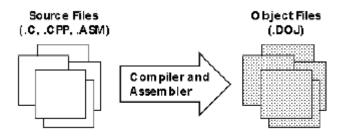

- 4.3.1 Compiling e Assembling

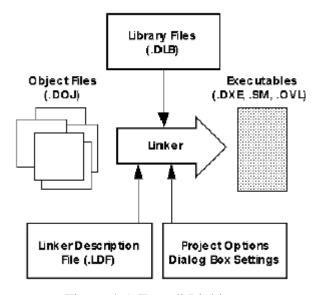

- 4.3.2 Linking

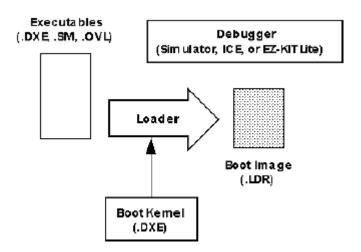

- 4.3.3 Loading e Splitting

- 4.4 Mappa di memoria

- 4.5 Organizzazione memorie

- 4.6 Processo di boot

- 4.7 Descrizione codice

- 4.7.1 Programmazione e Configurazione DSP e periferici

- 4.7.2 Interrupt e API per UART

- 4.7.3 Compressione JPEG e de-Intelacciamento

- 4.7.4 Driver FLASH M29W160EB

## 4.7.5 Protocollo Xmodem

## 5. Conclusioni

Appendice A Schemi Elettrici Appendice B PCB Appendice C Codice Sorgente

Bibliografia

# **Sommario**

Il progetto PICPOT, PICosatellite del POlitecnico di Torino, è nato nel Gennaio 2004 con lo scopo di costruire nell'arco di un anno un picosatellite universitario, di massa minore di 1 kg ??, con finalità educative e di ricerca; PICPOT è inserito in un progetto più ampio, costituito da una costellazione di satelliti universitari italiani, attualmente in via di definizione. Il progetto del satellite si è basato su diversi requisiti, quali forma cubica con lato di 13 cm, massa inferiore ad 2 kg, potenza non superiore a 1.5 W, almeno 90 giorni di vita, orbita LEO (Low Earth Orbit) e compatibile con il lanciatore POD (Pico Orbital Deployer).

PICPOT ha come obiettivi quelli di verificare il funzionamento di componenti COTS (Components Off The Shelf) nello spazio, trasmettere dati telemetrici (temperature, tensioni, correnti, etc...) alla stazione di Terra e scattare delle fotografie dallo spazio. La sua struttura esterna definitiva è un cubo di sei facce quadrate ed ortogonali tra loro, ricoperto di cinque pannelli solari, dotato esternamente di due antenne (2.4 GHz, 435 MHz), tre fotocamere, due kill-switch ed un connettore di test.

La parte elettronica del satellite è formata da 6 schede che sovraintendono alle varie funzioni previste; nel seguito viene data una breve descrizione di ciascuna scheda:

- *PowerSupply*: mantiene cariche le batterie ricaribili del satellite e controlla lo stato elettrico e termico dei pannelli, dei caricabatteria e delle batterie stesse.

- *PowerSwitch*: alimenta le altre schede generando le tensioni necessarie a partire dalle tensioni delle batterie.

- Tx/Rx: trasmette e riceve i segnali tra il satellite PICPOT e la stazione di Terra, alle frequenze di 435 MHz e 2.4 GHz nella banda dedicata alle comunicazioni satellitari amatoriali.

- *ProcA* e *ProcB*: elaborano i dati ricevuti da Terra e trasmettono le fotografie e la telemetria del satellite, alle due diverse frequenze. Le due schede, ognuna dotata di un microprocessore, hanno funzioni simili duplicate per ridondanza.

- Payload: acquisisce le immagini dalle tre fotocamere, le comprime in formato JPEG e le trasmette su richiesta ad uno dei due microprocessori di bordo.

Il lavoro svolto in questa tesi riguarda in particolare il progetto hardware e software, la realizzazione e il collaudo della scheda Payload. Nella sua versione definitiva essa adotta un Digital Signal Processor (DSP) a 16 bit prodotto da Analog Devices, chiamato Blackfin, che può raggiungere la massima frequenza di clock di 400 MHz. Il sottosistema di memorizzazione include

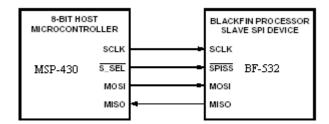

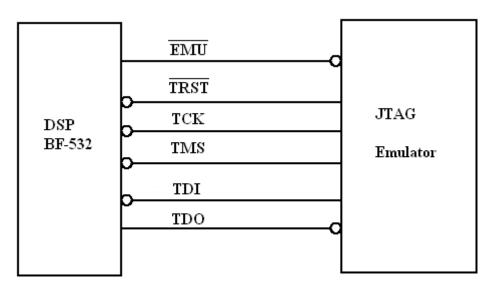

una memoria SDRAM da 8 Mbyte, una memoria SRAM da 2 Mbyte e una memoria FLASH non volatile da 2Mbyte. Inoltre per l'acquisizione delle foto, il processore è interfacciato, mediante una porta parallela a 8 bit dedicata, ad un decoder video, il quale converte in digitale il segnale analogico PAL proveniente dalle videocamere e lo codifica in un formato standard chiamato ITU-R BT.656-4. Il collegamento con i due processori di controllo delle schede ProcA e ProcB avviene tramite porte seriali, rispettivamente asincrona (UART) e sincrona (SPI). Per la programmazione e il debug è presente un'interfaccia JTAG.

Il progetto della scheda è iniziato da un'attenta fase di analisi delle specifiche richieste, riportate sul documento di descrizione del sistema, cercando di capire quali tipi di componenti fossero necessari, in relazione soprattutto ai vincoli ambientali previsti e all'interazione dei componenti con raggi cosmici o ioni pesanti presenti alla quota del satellite. Per esempio, una delle decisioni prese in questa fase riguarda la selezione della memoria che contiene il programma da eseguire sul DSP, in cui uno dei requisiti fondamentali è la robustezza rispetto a errori e/o modifiche accidentali su singoli bit, per garantire il buon funzionamento del sistema. Dopo attente ricerche, è stata quindi selezionata una memoria FLASH a gate NOR.

Il passo successivo è stato quello di cercare sul mercato dei componenti commerciali in grado di rispondere alle esigenze di progetto principali, nell'ottica del sistema in cui dovrà funzionare e delle condizioni ambientali interne; l'aspetto del consumo di potenza assume un ruolo di fondamentale importanza, sia perché l'intero sistema è alimentato esclusivamente da batterie con limitato contenuto energetico, sia a causa della ridotta capacità di dissipazione della potenza sotto forma di calore data l'assenza di atmosfera a 600 km dalla superficie terrestre. Altri requisiti ricavati dalle specifiche per il processore riguardano la presenza di una porta video compatibile con quella implementata sul decoder adottato, un DMA controller per l'acquisizione dell'immagine e una struttura ottimizzata per le operazioni più complesse e lunghe che avrebbe dovuto eseguire, cioè la compressine JPEG. Per questo ultimo motivo ci si è indirizzati verso l'adozione di un DSP. La scelta dei componenti è anche condizionata dalla loro disponibilità e reperebilità presso i distributori utilizzati dal progetto PICPOT, quali DigiKey, RS Components e Farnell.

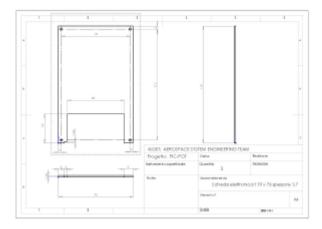

Definita l'architettura di sistema e scelti i componenti da adottare, la fase successiva è consistita nel progetto schematico e nel disegno del circuito stampato (PCB) della scheda, utilizzando il pacchetto software CAE (Computer Aided Design) di Mentor Graphics. Ogni componente inserito nel database è caratterizzato da due viste distinte: un simbolo logico e una cella fisica. La prima viene utilizzata a livello schematico, mentre la seconda, che definisce le dimensioni del package e la sua occupazione di area sulla scheda (footprint) viene usata per creare il PCB.

Dopo aver ordinato i componenti, coordinandoli con quelli utilizzati dalle altre schede, e aver mandato a fabbricare il PCB attraverso i files gerber, si è passati alla fase di montaggio e saldatura dei componenti sulla scheda. Questa operazione è stata molto delicata data la compattezza dei package adottati, tutti di tipo SMD, con distanza minima tra i piedini in certi casi pari a 0.5mm. La scheda montata è stata quindi collaudata mediante piccoli programmi di test appositamente sviluppati.

Lo sviluppo del software si è avvalso inizialmente di una scheda di valutazione dimostrativa prodotta da Analog Devices, ma ha poi avuto un forte impulso una volta resasi disponibile la prima scheda prototipo, in quanto alcuni dei componenti periferici utilizzati erano diversi. Allo scopo di ottenere un sistema perfettamente funzionante, nella prima stesura del software ci si è concentrati soprattutto sulla corretta inizializzazione dei registri di configurazione del core e delle diverse periferiche del processore, quali PLL, DMA, interrupt, UART e controller per memorie sincrone e asincrone.

Non essendo possibile la comunicazione con le schede ProcA e ProcB, perché non ancora disponibili, si è creato un canale di comunicazione tra la scheda e il PC, alternativo alla porta JTAG. Si è infatti implementato un driver per la porta UART per la comunicazione serial RS-232 e per il trasferimento bidirezionale PC – Payload di file o stream di dati utilizzando il protocollo Xmodem. Ciò ha permesso in parte di emulare la presenza delle altre schede del sistema satellite.

Si è testata quindi tutta la catena d'acquisizione video. Le immagini acquisite dalle videocamere vengono inizialmente immagazzinate in memoria nel loro formato originale, costitutio da due field interlacciati aventi un campione di luminanza per ogni pixel e due campioni di crominanza per ogni quadretto 2x2 di pixel (formato YCrCb 4:2:0). Il software esegue perciò le seguenti funzioni: 1) deinterlacciamento; 2) up-sampling della risoluzione della crominanza; 3) compressione in formato JPEG. Per quest'ultimo passo si è sfruttata una libreria liberamente disponibile di funzioni per la manipolazione e la trasformazione di immagini JPEG, opportunamente sfrondata da quanto non necessario e ottimizzata per l'esecuzione sul DSP.

Tutte le operazioni sopra elencate vengono eseguite, per ragioni di prestazioni, in memoria RAM. Il risultato dell'elaborazione, cioè l'immagine JPEG, deve però essere memorizzata in modo permanente in attesa della sua successiva trasmissione. Si è quindi sviluppato un driver per la memoria FLASH adottata, partendo da un codice sorgente fornito dalla ST Microelectronics. Anche questo codice è stato modificato e adattato alle esigenze della scheda Payload, per poi poter salvare sulla memoria FLASH sia le immagini JPEG che il programma da eseguire.

Il progetto della parte hardware è concluso e completamente testato mediante la simulazione delle diverse fasi di funzionamento che richiedevano l'utilizzo di tutti i componenti presenti sulla scheda,

mentre per quanto riguarda la parte software, è stata sviluppata la parte utile ad acquisire, comprimere e trasmettere via UART le foto JPEG, ma comunque deve essere completata la parte di coordinamento con le altre schede, soprattutto per quanto riguarda l'analisi dei telecomandi e l'interfaccia SPI.

# Capitolo 1

# **Introduzione**

## 1.1 Il progetto PICPOT

Il progetto PICPOT, PICosatellite del POlitecnico di Torino, è nato nel Gennaio 2004 con l'obiettivo di costruire nell'arco di un anno un picosatellite universitario, con una massa minore di 1 kg, a scopo educativo e di ricerca.

Il punto di partenza del progetto è stato il concetto di Cubesat.

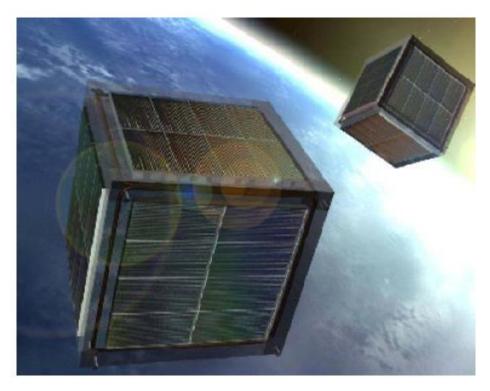

Figura 1.1 Prototipo di Cubesat ideato dalla CalPoly e dalla Stanford University

Cubesat significa satellite di forma cubica ed è nel contempo una filosofia progettuale.

E' uno standard per picosatelliti sviluppato nel 2001 dal Professore Robert Twiggs, docente alla Stanford University, USA, in collaborazione con la Space Systems Development Laboratory (SSDL) della Stanford University e la California Polytechnic State University, USA, per permettere

alle Università che intendono partecipare a questa sperimentazione di realizzare il proprio satellite e di mandarlo nello spazio a costi contenuti.

Un Cubesat è una scatola di forma cubica di 10 cm di lato e con una massa di 1 kg la cui struttura `e definita in funzione dell'adattamento al lanciatore POD (Picosatellie Orbital Deployer).

L'idea alla base di Cubesat è dunque quella di permettere agli studenti dei vari Dipartimenti di Ingegneria di cooperare per la realizzazione di un progetto globale che richiede nel contempo ottime conoscenze in campo ingegneristico e capacità sviluppate di risolvere di problemi di natura interdisciplinare.

L'idea di progettare un satellite è stata adottata da numerose Università italiane e straniere, fra le quali citiamo l'Universitat Wurzburg,(D), la Norwegian University of Science and Technology (NO), l'Aalborg University (DK) e l'Universit'a della Sapienza(IT).

Successivamente il Politecnico di Torino si `e impegnato a partecipare alla progettazione ideando PICPOT e collocandolo in un progetto più ampio, quello di una costellazione di satelliti universitari italiani, attualmente in via di definizione.

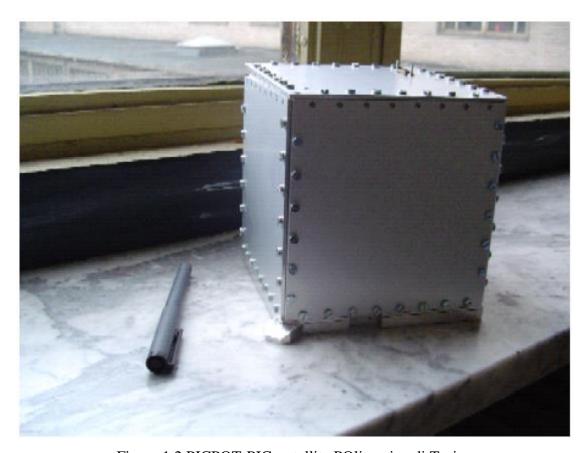

La figura 1.2 `e una fotografia della parte esterna del satellite, progettata e costruita dagli studenti del Dipartimento di Ingegneria Areonautica e Spaziale del Politecnico di Torino.

Figura 1.2 PICPOT-PICosatellite POlitecnico di Torino

Il progetto del satellite si è basato sui seguenti requisiti:

- forma cubica con lato di 13 cm

- massa inferiore ad 2 kg

- potenza non superiore a 1.5 W

- almeno 90 giorni di vita

- orbita LEO

- compatibilie con il lanciatore POD

Inizialmente PICPOT aveva come obiettivi quelli di verificare il funzionamento di componenti COTS (Components Off The Shelf) nello spazio, trasmettere dei dati alla stazione di Terra, scattare una o più fotografie e valutare il funzionamento del GPS in orbita LEO.

Per motivi economici e di tempo, non `e stato possibile dotare il satellite del GPS ma questo verrà realizzato in una delle prossime versioni.

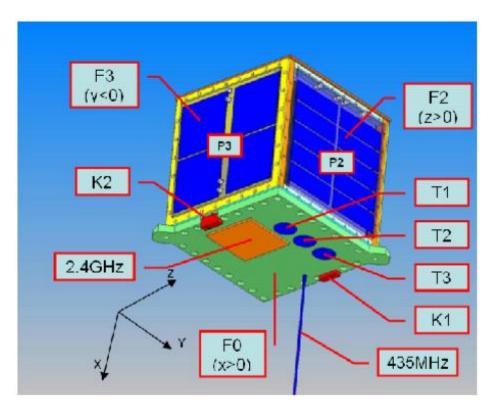

Nella figura 1.4 è rappresentata la struttura esterna definitiva di PICPOT: è un cubo dotato di sei facce quadrate ed ortogonali tra loro, di circa 13 cm di lato, ricoperto di pannelli solari (P1, P2, P3, P4, P5) e dotato esternamente di due antenne (2.4 GHz, 435 MHz), tre fotocamere(T1, T2, T3), due kill-switch (K1, K2) ed un connettore di test.

Figura 1.3 PICPOT-vista esterna

La parola chiave per capire l'idea alla base della struttura del satellite è ridondanza:

si è cercato infatti, dove possibile, di duplicare ogni sottosistema per evitare che il guasto di una singola parte compromettesse il funzionamento dell'intero satellite.

Le celle solari, ad esempio, sono di due tipi differenti, come si vede nella figura 1.3, proprio per motivi di ridondanza.

La comunicazione, inoltre, avviene su due canali indipendenti e mutualmente esclusivi:

quella assosciata alla frequenza di 435 MHz è gestita esclusivamente dal processore ProcA mentre quella associata alla frequenza di 2.4 GHz è gestitita esclusivamente dal ProcB. I due processori sono indipendenti e non comunicano tra loro.

Le antenne sono un'antenna patch per la frequenza intorno ai 2.4 GHz progettata apposta per il satellite ed un'antenna a dipolo per la frequenza intorno ai 435 MHz, di tipo commerciale.

I kill-switch sono montati su richiesta del lanciatore e garantiscono l'isolamento elettrico del satellite al momento del lancio.

L'oggetto di questa tesi è il progetto della scheda Payload che ha il compito di gestire le tre telecamere e, in particolare, di scattare delle fotografie in seguito ad una richiesta da parte della stazione di Terra. L'uso delle fotocamere non è funzionale ad un rilevamento di tipo scientifico, ma ha invece due obiettivi, uno di carattere didattico-educativo e l'altro di verifica del funzionamento di componenti COTS nello spazio, come il progetto dell'intero satellite richiede.

La parte elettronica del satellite è formata da una scheda PowerSwitch, da una scheda PowerSupply, da una scheda Tx/Rx e dai tre processori di bordo, ProcA, ProcB e Payload.

La scheda PowerSupply ha il compito di mantenere cariche le batterie ricaricabili del satellite e di monitorare lo stato elettrico e termico dei pannelli, dei caricabatteria e delle batterie stesse.

La funzione principale della scheda PowerSwitch è quella di alimentare le altre schede generando le tensioni necessarie a partire dalle tensioni delle batterie.

La scheda Tx/Rx ha la funzione di trasmissione e ricezione di segnali tra il satellite PICPOT e la stazione di Terra ideata a tale proposito, alle frequenze di 435 MHz e 2.4 GHz nella banda dedicata alle comunicazioni satellitari amatoriali.

I due processori, ProcA e ProcB, progettati ciascuno da un diverso studente, svolgono funzioni simili alle due diverse frequenze, ma sono stati duplicati per motivi di ridondanza, come spiegato in precedenza.

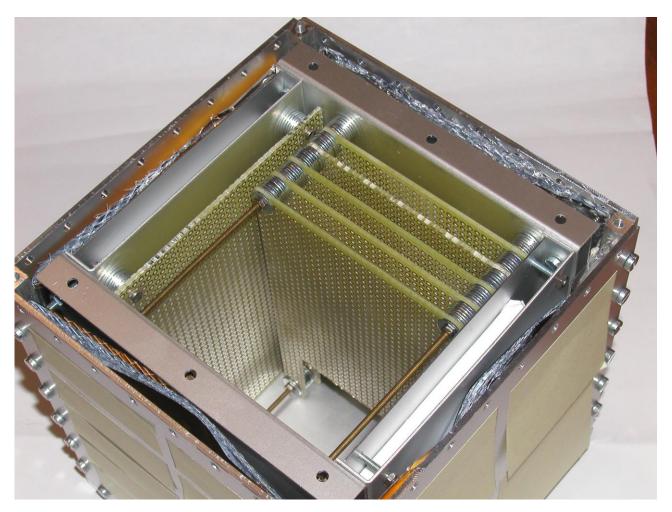

La figura 1.4 è una fotografia della parte interna di PICPOT che evidenzia la disposizione delle schede elettroniche e delle tre fotocamere.

Figura 1.4 PICPOT-vista interna

## 1.2 Vincoli ambiente spaziale

Uno degli aspetti più importanti tenuti in considerazione nel progetto di tutto il sistema PICPOT è stato l'ambiente dove esso sarebbe dovuto funzionare: lo spazio.

Lo spazio libero presenta alcuni importanti aspetti legati al funzionamento dei circuiti integrati, quali i raggi cosmici. I Raggi Cosmici sono delle particelle prodotte dalle reazioni termonucleari che possono avvenire in alcuni fenomeni celesti, come l'esplosione di supernovae, i fenomeni di collassi stellari o direttamente all'interno delle stelle stesse. Essi sono particelle subatomiche e fotoni ad alta energia, che bombardano costantemente la Terra da ogni direzione. Le energie di queste particelle ricoprono un vasto intervallo fino ad arrivare oltre 1020eV. Tali raggi sono quindi, particelle provenienti dallo spazio, che, interagendo con gli atomi presenti nell'atmosfera, producono un alto numero di particelle che arrivano fino a terra.

Per sistemi orbitanti attorno alla terra, come i satelliti per le telecomunicazioni, la prima sorgente di radiazione sono gli elettroni ed i protoni intrappolati dalla magnetosfera terrestre e sono di interesse

rilevante ad altitudini comprese fra 1000Km e 32000Km. La loro estensione è in realtà maggiore, ma il livello del flusso di particelle diminuisce rapidamente al di fuori di questo range di altitudine.

Le distribuzioni in altitudine per protoni ed elettroni, sono significativamente diverse fra loro, ma entrambe sono accomunate dal fatto che sia per gli elettroni che per i protoni, le particelle più energetiche si trovano ad altitudini maggiori.

I dispositivi elettronici impiegati nella fabbricazione di satelliti ed apparati spaziali di volo, devono normalmente rispondere ai requisiti normativi definiti ed emessi dalle agenzie spaziali NASA ed ESA. Per quanto non previsto in questi requisiti, ci si riferisce di regola alle specifiche MIL applicabili al settore avionico-spaziale. Questo perché i dispositivi elettronici al silicio sono particolarmente sensibili alle radiazioni cosmiche e possono cessare di funzionare se queste superano particolari livelli energetici, anche in dipendenza dalla tecnologia di fabbricazione utilizzata. Anche questi aspetti di resistenza alle radiazioni cosmiche sono regolamentati dalle normative sopra citate; queste prevedono per le differenti applicazioni l'uso di componenti definiti nel linguaggio tecnico "rad-hard" o "radtollerant".

I componenti rad-hard sono normalmente in grado di funzionare anche se esposti a radiazioni di livello fino a 100krad, ed in alcuni casi fino a 300krad; per quelli rad-tollerant i livelli si riducono rispettivamente a 10krad e 30krad. Dispositivi certificati resistenti alle radiazioni, per come sopra esposto, in accordo con la normativa hanno un costo fino a 1000 volte quello dell'equivalente dispositivo qualificato per uso industriale. La reperibilità sul mercato di materiali con queste caratteristiche richiede tempi di consegna che vanno tipicamente da 6 a 24 mesi.

Quanto esposto è in fortissimo contrasto con lo sviluppo del mercato spaziale, che richiede già oggi la fabbricazione di apparati e satelliti in soli 6 mesi dall'emissione di un ordine (mercato spaziale commerciale) ed a costi sempre più bassi.

Il progetto PICPOT che si basa sull'utilizzo di componenti commerciali COTS (Components Off The Shelf) rappresenta una sfida alle considerazioni precedenti. Infatti, sebbene il satellite orbiterà in un'orbita bassa, circa 600 Km, sicuramente potrà risentire di queste radiazioni, per questo numerose scelte di progetto sono state fatte in funzione di questo.

Tra le principali conseguenze dell'interazione delle radiazioni cosmiche con i dispositivi a semiconduttore vi sono gli effetti di danneggiamento ad evento singolo (SEE). Questo tipo di danneggiamento riguarda l'azione di una singola particella che attraversa il substrato dei circuiti.

Tali effetti devono la loro importanza al notevole aumento della miniaturizzazione dei dispositivi elettronici.

I single event effect sono di diverso tipo e possono essere distinti, in effetti transitori ed effetti permanenti. In alcuni casi gli effetti permanenti possono essere così disastrosi da causare la rottura totale del dispositivo.

Per i diversi effetti ad evento singolo si può fare la seguente classificazione:

- Effetto transitorio: SEU ovvero single event burnout.

- Effetto permanente: SEL, single event latchup; SEB, single event burnout e SEGR, single event gate rupture ed altri effetti ad evento singolo.

### 1.2.1 Single event upset

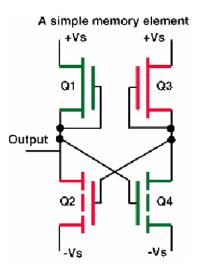

Quando si verifica un single event upset, quello che accade è che ioni pesanti depositano una tale quantità di energia su un elemento bistabile, da causarne il cambiamento di stato logico. Tali effetti sono facilmente osservabili in memorie non protette. La figura 1.5, mostra un esempio di SEU su un dispositivo elettronico.

Figura 1.5: SEU su un dispositivo a un bit

Il circuito è disegnato in modo da avere due stati stabili rappresentati reciprocamente con "0" ed "1". Per ogni stato due transistor vengono commutati on ed off. Un SEU avviene quando una particella energetica che attraversa il dispositivo fa cambiare stato al transistor.

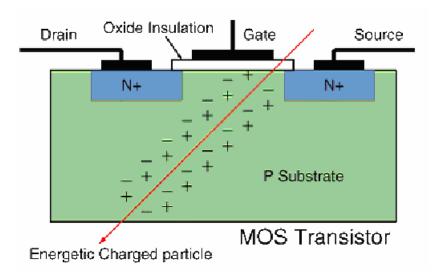

Figura 1.6: generazione di spike di corrente a causa di effetti SEU nei MOSFET

La figura 1.6 mostra, invece, come la particella energetica che penetra nel dispositivo genera un segnale elettrico spurio. La particella produce, infatti, cariche durante il suo percorso sotto forma di elettroni e lacune, che si addensano al source ed al drain e generano un impulso di corrente.

#### 1.2.2 Single event latchup

Un single event latchup è un percorso anomalo di corrente, prodotto fra strutture n-p-n o p-n-p, che sparisce soltanto nel momento in cui viene rimossa l'alimentazione dal dispositivo. Tale problema affligge la maggior parte dei dispositivi microelettronici.

Si ha un latchup quando una particella carica che transita nel dispositivo, induce una corrente tale da aumentare la corrente operativa oltre le specifiche del dispositivo e notevolmente superiore a quella incontrata nelle normali operazioni.

Questo effetto è potenzialmente distruttivo perché la corrente aumenta oltre le specifiche per cui il dispositivo è realizzato, quindi se il dispositivo non viene protetto o limitato in corrente rischia di subire un danneggiamento irreparabile o comunque riduce notevolmente le sue prestazioni peggiorando notevolmente le sue specifiche di funzionamento.

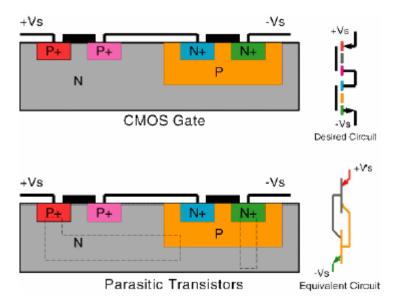

Figura 1.7: schema di un latchup CMOS

Un latchup nei circuiti digitali può avvenire anche quando un impulso spurio di corrente, come quelli prodotti dai raggi cosmici, attiva il transistor parassita presente nella tecnologia CMOS, che nelle normali condizioni operative è fuori uso. Il risultato che si ottiene è che il dispositivo permane nello stato di On. Si parla di transistor parassiti, perché il bulk dei CMOS contiene due transistor bipolari parassiti che formano una struttura a quattro layer.

Figura 1.8: schema di una cella CMOS

Le sorgenti di latchup nei CMOS non sono contenute nelle normali operazioni di tali dispositivi ma, segnali transitori posti ai terminali di ingresso o di uscita li possono inavvertitamente triggerare portandoli nella condizione di On.

Quando i transistor parassiti sono attivi, pilotano correnti molto grandi che possono provocare danni anche permanenti. Una volta che il dispositivo è andato in latchup la struttura a quattro layer è

portata in conduzione continua; da questa condizione si esce soltanto se viene rimossa l'alimentazione in un tempo dell'ordine di millisecondi.

Durante il latchup le correnti possono essere molto elevate dell'ordine delle centinaia di milliampere o maggiori, tali correnti circolando nel dispositivo ne aumentano la temperatura. Tali aumenti di temperatura non solo possono danneggiare il circuito, ma possono far si che il latchup si estenda ad altre regioni che prima non ne erano interessate.

Proprio per le sue potenzialità distruttive, il latchup si pone come un grave problema per i sistemi spaziali.

# Capitolo 2

# **Progetto Hardware**

## 2.1 Specifiche scheda Payload

La scheda Payload è una delle schede processore presente su PICPOT, la quale si occupa di gestire le tre videocamere presenti al fine di ottenere delle foto della terra durante il passaggio nella zona in vista del satellite.

Il progetto della scheda Payload è iniziato dalle seguenti specifiche:

- Acquisire un'intero fotogramma da una tra le tre diverse videocamere presenti sul satellite di lunghezza focale diversa e con uscita analogica in formato PAL.

- Codificarlo in formato digitale.

- Campionarlo e comprimerlo in formato JPEG.

- Trasmetterlo ad uno dei due processori presenti sul satellite che gestiscono la trasmissione a terra dell'immagine.

- Permettere il caricamento e l'esecuzione di un programma esterno proveniente da terra.

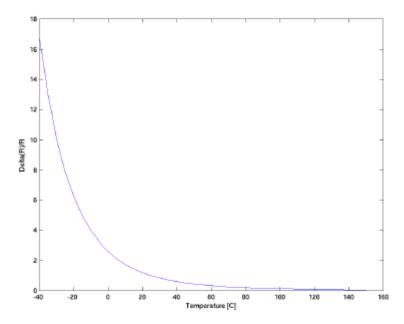

- Permettere l'acquisizione della temperatura della scheda Payload da parte delle schede ProcA e ProcB

La scheda sarà totalmente comandata mediante diversi telecomandi codificati dai due processori alternativamente, con due canali di comunicazione distinti e dalla scheda PowerSwitch che fornisce le alimentazioni necessarie al funzionamento dei componenti della scheda.

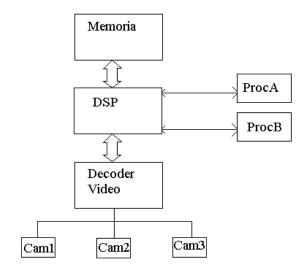

Al fine di soddisfare tale specifiche si è partiti con un progetto di massima della scheda, ipotizzando un processore centrale affiancato da una memoria su cui memorizzare l'immagine da comprimere e quella compressa; inoltre il processore dovrà avere almeno due porte di comunicazione hardware standard distinte, compatibili con quelle presenti sui due processori con cui la scheda dovrà comunicare. Infine essendo tre le videocamere, il processore dovrà avere a disposizione un certo numero di pin general purpose, utilizzabili come segnali di scelta della videocamere e magari alcuni segnali di controllo. Infine dato che le videocamere forniscono un segnale analogico in uscita bisognerà riportarlo in un formato digitale tramite un video decoder e poi acquisire i dati col processore.

Il seguente schema a blocchi descrive lo schema di principio della scheda Payload al fine di soddisfare tali specifiche:

Figura: 2.1 Schema a blocchi specifiche scheda Payload

## 2.2 Scelta dei componenti

#### 2.2.1 Criteri di scelta dei componenti

Il progetto della scheda Payload si è basato dapprima su alcune considerazioni sull'ambiente in cui avrebbe dovuto funzionare, ossia all'interno di un satellite di dimensioni ridotte quindi di un sistema alimentato da batterie caricate mediante pannelli solari; il consumo energetico della scheda è il fattore principale che è stato tenuto in considerazione nel progetto. Legato ad esso vi è infatti un forte interesse a non far surriscaldare troppo i componenti durante il loro funzionamento, dato che l'unica modalità di dissipazione del calore a 600 Km di altitudine è l'irraggiamento e la conduzione dei piani di alimentazione, quindi di bassa efficienza.

Altro fattore importante per alcune scelte di progetto è stato la possibile interazione dei componenti di tecnologia CMOS, con particelle pesanti presenti nello spazio esterno alla nostra atmosfera, creando la possibilità di effetti di latchup in circuiti CMOS. Tale effetto può condizionare sia i dati memorizzati nelle memorie, sia le correnti erogate da regolatori di tensione, sia i valori di alcuni MOS integrati utilizzati come switch per alimentazioni. Da questo punto di vista inoltre, è stato fondamentale un accurato calcolo dei consumi di corrente massimi da parte della scheda nelle varie fasi di funzionamento, al fine di poter permettere ai progettisti della scheda PowerSwitch di realizzare dei circuiti che staccano l'alimentazione alla scheda in presenza di picchi di assorbimento di corrente, denominati circuiti anti-latchup, adeguati al normale assorbimento della scheda.

Un'ulteriore caratteristica di sistema che ha caratterizzato la scelta dei componenti è che la scheda Payload viene attivata dalla scheda PowerSwitch, la quale fornisce l'alimentazione al sistema dato il comando che le proviene da uno dei due processori che gestiscono tutto il sistema.

Quando la scheda payload deve svolgere qualche operazione essa viene accesa interamente, ma essa non usa mai tutti i circuiti integrati presenti su di essa contemporaneamente, quindi è importante che essi presentino una modalità di Power Save con un bassissimo consumo di potenza, affinché l'integrale nel tempo dell'energia assorbita dal componente quando non è utilizzato sia molto basso, dato che magari la scheda può rimanere accesa quasi un minuto ininterrottamente (da specifiche di sistema). Nella scheda quindi sono state studiate delle soluzioni affinché ogni componente non utilizzato venisse portato in Power Save Mode.

Infine anche il lato economico ha avuto un certo peso nelle scelte effettuate, favorendo la scelta di prodotti disponibili sotto forma di samples gratuiti in quantità adeguate, in modo da permettere l'utilizzo di soli samples per la prototipazione e le schede definitive.

#### 2.2.2 Componenti Video

I componenti video presenti sulla scheda Payload sono le videocamere e il decoder video.

Le videocamere da utilizzare sono state scelte svolgendo dapprima su delle considerazioni sulla tipologia di sensore da utilizzare. Esistono in commercio due tipi di sensori per videocamere:

- Sensori CMOS (Copper Metal Oxide Semiconductor)

- Sensori CCD (Charge Coupled Devices)

I sensori di tipo CCD rispetto ai sensori CMOS sono molto più sensibili, ossia forniscono alla videocamera la capacità di fornire immagini di buona qualità anche a basse condizioni di luce. Questo inoltre è anche associato ad un miglior rapporto segnale/rumore rispetto ai sensori CMOS, i quali a causa delle correnti di leakage presentano una maggiore interferenza di base, che diventa subito importante a bassi valori di illuminazione. Inoltre la risposta di un CCD è indipendente dall'intensità luminosa incidente; infatti, i sensori CCD sono dei rivelatori perfettamente lineari (la linearità è di solito migliore dello 0.01%). In pratica ciò significa che il numero di elettroni generati in un pixel è direttamente proporzionale alla quantità di luce incidente. Tutto questo comporta quindi una maggiore dinamica del sensore CCD.

I vantaggi tipici del sensore CMOS è il prezzo contenuto dato che sono prodotti nelle stesse fonderie da produttori di circuiti integrati, il cui numero prodotto fa quindi scendere notevolmente il costo; inoltre il sensore CMOS presenta un basso assorbimento di potenza rispetto a sensori CCD.

Questi due parametri sono due dei criteri fondamentali delle nostre scelte di progetto, ma il parametro di costo è ininfluente dato che le videocamere sono state cortesemente fornite dalla ITEM s.r.l. ed inoltre rese disponibili in package sotto vuoto per essere messe all'interno del satellite; inoltre sono state anche fornite tre videocamere campione per il debug e i test in laboratorio della scheda Payload.

Infine il parametro di consumo di potenza è relativo in quanto il nostro scopo non è registrare uno stream video di lunga durata, che quindi significherebbe un notevole consumo di energia ma consiste nell'acquisizione di un solo fotogramma (dalla durata relativamente breve di circa 50ms), che quindi sebbene il consumo di potenza istantanea di una videocamera basata su sensore CCD sia importante, l'energia consumata è comunque molto piccola dato che essa viene accesa e poi spenta solo per l'acquisizione della foto.

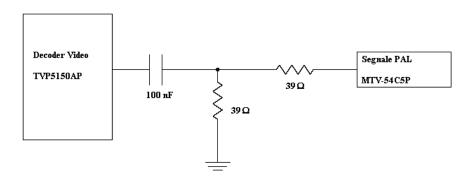

Quindi si è deciso di utilizzare tre videocamere basate su sensore CCD, di lunghezza focale diversa e quindi angoli di ripresa diversi, denominate MTV–54C5P. Inoltre queste videocamere sono intrinsecamente analogiche e quindi il segnale uscente è in formato analogico televisivo PAL.

Date le caratteristiche delle videocamere adottate, il segnale analogico PAL uscente bisognava che fosse convertito in digitale e codificato in un formato standard, possibilmente implementato in un processore per l'elaborazione numerica dei segnali presente in commercio.

Infatti in commercio sono presenti componenti integrati denominati "Decoder Video", i quali convertono in digitale uno o più canali analogici PAL o NTSC in ingresso e li codificano in un formato standard per il segnale televisivo digitale chiamato ITU-R BT.601-4. Il segnale televisivo digitale così codificato viene poi reso disponibile su 8 bit secondo un formato standard d'interfaccia di segnali video chiamato ITU-R BT.656-4.

Il decoder video è stato selezionato in base ai problemi principali a cui è sottoposto il sistema, presentati in precedenza; inoltre è stato preso in considerazione il numero di canali d'ingresso video analogico disponibili, in quanto la scheda deve gestire tre videocamere. I decoder video standard in commercio presi in considerazione sono stati di due tipi:

- con 6 canali d'ingresso analogico

- con 1 canale d'ingresso analogico

Il primo tipo aveva il pregio di permette l'ingresso dei tre canali in tre ingressi distinti e di poterli selezionare internamente, a fronte dell'altra soluzione che obbligava ad avere le videocamere in parallelo sul segnale video. Quest'ultimo però non risultava un problema perché il datasheet delle video camere garantiva alta impedenza sul segnale video in mancanza di alimentazione; inoltre, il segnale analogico PAL uscente dalle videocamere è di 1V picco-picco (da datasheet) mentre quello

accettato in ingresso dal decoder video del secondo tipo è 0,75V picco-picco. Il segnale dovrà essere partizionato obbligatoriamente, quindi la presenza di altre 2 videocamere in parallelo saranno solo un impedenza in parallelo a quella di partizione, non comportando grandi problemi dato che anche misure effettuate in laboratorio hanno dato un'alta impedenza d'ingresso a dispositivo spento. Inoltre l'alimentazione per le tre videocamere sarebbe stata comunque da selezionare, perché dato che tutte e tre le video camere sarebbero state alimentate dalla stessa linea a 12V proveniente dalla PowerSwitch, solo una doveva essere alimentata per l'acquisizione della foto.

Dato che il decoder video a un canale analogico in ingresso sembrava la miglior soluzione, anche a fronti di consumi ridotti e package più compatti, il decoder video adottato è denominato TVP5150A prodotto dalla Texas Instruments.

Dato che questo componente viene solo utilizzato nella fase di acquisizione dell'immagine dalle videocamere (dalla durata relativamente breve di circa 50ms), ma non nella fase di compressione JPEG e nella fase di trasmissione dell'immagine definiva ai processori, sebbene esso rimanga acceso, quindi deve consumare il minimo di energia possibile. Infatti un'altra caratteristica fondamentale di questo componente è il bassissimo consumo di corrente in modalità Power Save, con un valore massimo stimato di 1µA. Nelle fasi in cui esso non viene utilizzato dal processore verrà messo in modalità di risparmio energetico tramite una porta logica OR sui tre segnali pilota delle alimentazioni delle videocamere (vedi seguito).

Infine questo decoder fornisce dopo il power-up un'interrupt quando avviene la sincronizzazione col segnale PAL, così che il processore dopo averlo ricevuto può iniziare a scaricare il fotogramma senza attendere ulteriore tempo e consumare energia invano (anche perché la potenza assorbita dalla scheda in questa fase risulta elevata data la presenza una videocamera accesa).

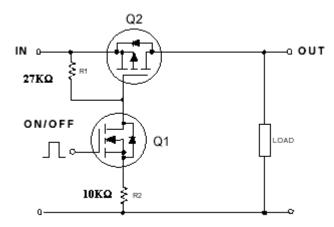

Al fine di poter selezionare l'alimentazione in modo distinto per le tre videocamere, la soluzione in linea di principio era quella di avere un mosfet in configurazione di pass transistor. Il problema di utilizzare un solo transistor è che il pilotaggio rimane in configurazione *high-side*, ossia il potenziale di riferimento del segnale pilota e quello del transistor sono diversi, uno il round e per l'altro il 12V. Quindi dato che i pin di I/O di un processore vanno da 0V a 3.3V, non era possibile pilotare un solo transistor. Quindi si è pensato di adottare una configurazione con un n-mos che pilota un p-mos come pass transistor, e pilotare con un pin del processore l'n-mos in configurazione *low-side*. Il sistema funziona se si pone una resistenza di pull-up tra il gate e il source del pass transistor che lo tiene chiuso se l'n-mos è aperto, quindi se il segnale pilota è a "0".

Tale circuito così realizzato lo si è trovato sotto forma di componente integrato in package estremamente piccolo prodotto dalla Fairchild, denominato FDC6324L. La stessa azienda ne

fornisce campioni per la prova del componente in quantità piuttosto cospicue, così tutte le schede realizzate monteranno samples della casa produttrice stessa.

#### 2.2.3 Processore

Come si nota dallo schema a blocchi in figura 2.1, il processore sarà il cuore di tutte le funzioni svolte dalla scheda Payload. Quindi dovrà integrare varie funzionalità sia di tipo standard, quali almeno due porte di comunicazione hardware standard e almeno un controller per memorie non volatili, in quanto dovrà essere memorizzato il programma per il funzionamento della scheda, sia più specifiche per applicazioni video, come una porta per l'acquisizione di stream video nel formato del decoder video selezionato, l' ITU-R BT.656-4. Inoltre come per ogni componente, il processore doveva essere comunque contenuto in dimensioni e nei consumi ma doveva essere adeguato alla funzionalità di calcolo principale per cui sarebbe stato usato: la compressione JPEG. Il compressore JPEG come si vedrà in seguito, ha alla base un calcolo di una trasformata coseno discreta, la quale prevede come operazione fondamentale la seguente:

$$X[k] = \alpha[k] \sum_{n=0}^{N-1} x[n] \cos \left( \frac{\pi (2n+1)k}{2N} \right) \qquad k = 0, 1, ..., N-1$$

Quindi moltiplicazioni e addizioni diventano le operazioni più frequenti e quindi quelle che devono essere ottimizzate per rendere più veloce possibile il calcolo della trasforamata coseno e la compressione di un intera immagine.

Dato che nei controllori o processori general-purpose, l'operazine di moltiplicazione richiede un elevato costo computazionale, risulterebbe più adatto un processore progettato per l'elaborazione numerica, chiamato DSP (Digital Signal Processor), dove la sua unità di calcolo ALU (Arithmetic Logic Unit) contiene una unità funzionale chiamata MAC (Multiply Accumulator), predisposta ad eseguire moltiplicazioni e addizioni in contemporanea, abbassando notevolmente il costo computazionale di una trasformata coseno discreta e quindi della compressione JPEG di un'intera immagine.

Dopo una attenta rassegna dei vari processori per sistemi embedded per applicazioni video presenti sul mercato, il processore adottato è denominato Blackfin e prodotto da Analog Devices. Questo recentissimo prodotto è stato scelto appunto perché soddisfava le esigenze della scheda Payload appena esposte.

Infatti il Blackfin utilizzato, nome in codice BF532, presenta una porta video ITU-R BT.656-4 a 8 bit, due controller per memorie esterne, quindi risultava possibile collegare una memoria non volatile su cui poter salvare il programma. Inoltre queste due funzionalità erano potenziate dalla presenza di un DMA (Direct Memory Access) controller, che permetteva il salvataggio dei dati video acquisiti dalla porta ITU-R BT.656-4 direttamente in real-time durante l'acquisizione su una memoria esterna mediante i controller interni.

Inoltre il Blackfin presenta due porte standard quali SPI (Serial Peripheral Interface) e UART (Universal Asynchronous Receiver Transmitter) oltre a due porte seriali generiche veloci bidirezionali che quindi garantivano la possibilità di avere due porte hardware distinte per avere due canali di comunicazione separati con i due processori sempre per l'obiettivo di avere ridondanza del sistema, nel caso uno dei due andasse perso, non influenzerebbe la comunicazione con l'altro.

Infine il Blackfin risulta essere un Digital Signal Processor (DSP), quindi adatto come spiegato in precedenza alle funzioni di compressione JPEG a cui è anche destinato mediante le sue potenti unità di calcolo che verranno illustrate in seguito.

#### 2.2.4 Memorie

Dalle specifiche del sistema Payload, si può notare come il ruolo delle memorie sia importante per le diverse funzioni che devono essere adempite. Inoltre esse rivelano come a seconda delle diverse fasi, possa essere più funzionale ed efficiente un certo tipo di memoria rispetto ad un altro.

La scelta di adottare il DSP Blackfin di Analog Devices, ha permesso un'ampia libertà di scelta sulle memorie, presentando due controller distinti, uno per memorie sincrone, quali SDRAM tipo PC100 e PC133, e uno per memorie asincrone, quali SRAM e FLASH.

La funzione principale delle memorie che devono essere adottate è quella di contenere il codice sorgente del programma utilizzato dal DSP in maniera sicura rispetto ai problemi legati all'ambiente spaziale, spiegati nel capitolo 1. Si è cercato quindi una memoria adatta a svolgere questa funzione, quindi non volatile, riprogrammabile on board e a basso voltaggio, e compatibile con la tipologia di memorie supportate dal processore.

Si è quindi scelto di utilizzare per svolgere tali funzioni una memoria di tipo FLASH.

Le memorie FLASH sono basate su due architetture:

- a porte NOR

- a porte NAND

A seconda dell'architettura utilizzata, queste memorie presentano diverse caratteristiche e differenti comportamenti in ambienti spaziali. Qui di seguito vengono riportate le principali caratteristiche che differenziano le due tipologie:

| FLASH Characteristics |                          |  |  |

|-----------------------|--------------------------|--|--|

| NOR                   | NAND                     |  |  |

| Low Density           | Higher Density           |  |  |

| Higher Cost/Bit       | Lower Cost/Bit           |  |  |

| Faster Random Access  | Faster Sequential Access |  |  |

| Not Scalable          | Scalable                 |  |  |

| Supplier Differences  | Single Standard          |  |  |

Figura 2.2: caratteristiche memorie FLASH

Le memorie OR sono le memorie FLASH più antiche e quelle più utilizzate per memorizzare sistemi operativi o sorgenti di BIOS. Questo data anche la loro bassa densità rispetto alle memorie FLASH a gate NAND che grazie alla loro densità riescono a raggiungere dimensioni enormi. Questo però è il loro principale svantaggio rispetto al tipo a gate NOR di fronte al problema delle radiazioni cosmiche perchè le FLASH NAND usano tipicamente 8 o 16 celle impacchettate in serie con una linea bit in comune. Questo rende più densa la memoria ma causa una maggiore sensibilità al danneggio a causa delle radiazioni, in quanto il leakage indotto dalle cariche ionizzate incidenti il dispositivo si sommano insieme.

In fase di progetto si cercato quindi di capire quale tipologia di memoria potesse soddisfare le specifiche di progetto e contemporaneamente essere più robusta rispetto ai vincoli ambientali dello spazio, spiegati nel capitolo 1.

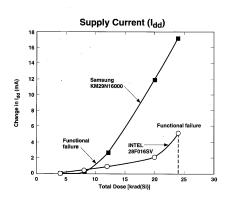

Si è utilizzato quindi una ricerca svolta dal California Institute of Technology, sugli effetti delle radiazioni cosmiche sui due tipi di memorie FLASH; infatti utilizzando una memoria FLASH a gate NOR prodotta da Intel e una memoria a gate NAND prodotta da Samsung hanno ottenuto i seguenti risultati:

irradiando i dispositivi accesi alla tensione di alimentazione (in questo caso 5V) a temperature ambiente, si è riscontrato una maggiore robustezza da parte delle memorie di tipo a gate NOR, come è possibile notare dal grafico seguente:

# No Charge Pump No Charge Pump Activated V<sub>p</sub> = 12V Intel NOR Structure (several power supply options) Samsung NAND Structure 5V Supply (charge pump always used)

**Total Dose Failure Levels**

Figura 2.3: risultati dopo il test d'irradiazione sul funzionamento delle memorie FLASH

• eseguendo lo stesso test e mappando l'andamento della corrente di alimentazione, si vede come la memoria FLASH a gate NAND sia molto più sensibile.

Figura 2.4: andamento della I<sub>dd</sub> delle FLASH dopo il test d'irradiazione

Le conclusioni della ricerca svolta sono che l'architettura di entrambe le tipologie delle memorie FLASH sono intrinsecamente robuste rispetto i single event upset (SEU); inoltre però, la tipologia a gate NOR risulta essere più robusta alle radiazioni ionizzate presenti nello spazio libero, sia in termini di energia incidente suportata, sia in termini di aumento della corrente di alimentazione. L'unico parametro che può variare in egual misura su entrambe le tipologie a causa dell'interazione con particelle ionizzate è il tempo di cancellazione e scrittura dei blocchi, ma comunque ininfluente per la scelta tra le due tipologie di memoria.

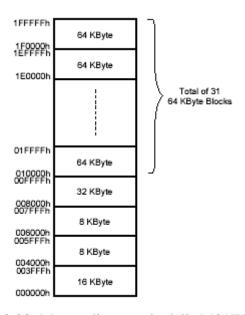

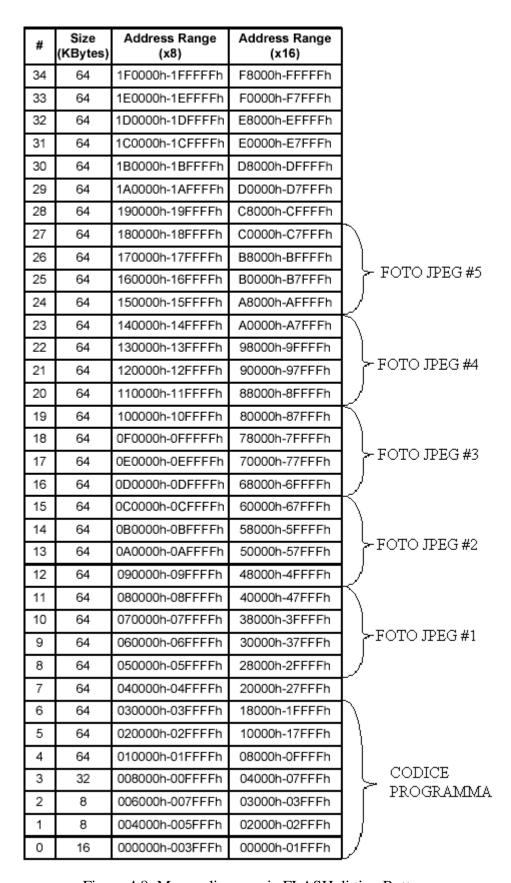

Si è quindi appreso tramite questa documentazione che le memorie FLASH a gate NOR risultavano essere più adatte alle specifiche della scheda Payload, non necessitando inoltre di memorie di elevate dimensioni, quali sono solitamente quelle di tipo NAND. Infatti si era calcolato in fase di progetto che la memoria FLASH dovesse quindi contenere il binario del software utilizzato dal

DSP, che doveva essere di al massimo 200 Kbyte, e al massimo 5 immagini compresse JPEG di dimensioni massime di 100 Kbyte ciascuna, per motivi di tempistiche nella trasmissione a terra dell'immagine da parte delle schede ProcA e ProcB. Inoltre si era previsto anche una possibile copia di backup del software da utilizzare nel caso di corruzione della copia principale e la possibilità di contenere una specie di look up table per la codifica dell'immagine compressa, non ancora ben definita in fase di progetto. Si necessitava quindi di almeno 1Mbyte di spazio, ma pe eesere sicuri si è cercato una memoria di dimensioni maggiori.

Si è quindi andati a cercare tra le memorie presenti in commercio e si è scelto di adottare la memoria FLASH NOR della STMicroelectronics denominata M29W160EB, da 2 Mbyte.

Oltre a soddisfare le nostre specifiche ed essere disponibile presso i fornitori utilizzati, questa memoria è stata adottata in quanto la STMicroelectronics rendeva disponibile un driver completo, scritto in linguaggio C e accompagnato da una descrizione dettagliata contenuta in un application note. Questi sorgenti sono stati utilizzati come base per sviluppare le funzioni necessarie nel nostro software per poter leggere e scrivere sulla memoria Flash utilizzata.

Inoltre la presenza di una memoria sul sistema Payload era richiesta dalla necessità di memorizzare l'immagine acquisita dalla porta video ITU-R BT.656-4. Il DSP Blackfin da la possibilità come spiegato in precedenza, di memorizzare l'intero fotogramma su una memoria esterna in real-time, quindi dato che la frequenza del segnale video del formato standard in uscita è di 27 MHz (si veda il sottocapitolo 2.3.2.1), il DSP acquisisce i dati via DMA controller con delle restrizioni nelle tempistiche della memoria destinazione. Questo quindi rende inutilizzabile la memoria FLASH per tale scopo perché intrinsecamente lenta, come verrà spiegato in seguito, quindi si è dovuto pensare di adottare un altro tipo di memoria.

Di fondamentale importanza è la considerazione che subito dopo l'acquisizione del fotogramma, lo si sarebbe compresso in un immagine JPEG e salvata in una memoria sicura (quale poteva essere la memoria di tipo FLASH, in quanto intrinsecamente insensibili al single event upset, SEU), tutto nello stesso ciclo di funzionamento, dove la scheda Payload sarebbe rimasta accesa per tutto questo periodo quindi anche una memoria volatile sarebbe andata bene.

Si aveva quindi la possibilità di scegliere tra memorie di diverso tipo della FLASH e anche volatili, tipo memorie sincrone SDRAM o memorie asincrone SRAM, entrambe supportate dal DSP adottato e utilizzabili come memoria destinazione esterna di un trasferimento di dati mediante il controller DMA, quindi adatte per l'acquisizione del fotogramma dalla porta video.

Seguendo uno dei principi base del progetto PICPOT, ossia di avere un sistema ridondante ove è possibile di un livello, ossia tollerante ad un guasto o malfunzionamento, si è deciso di adottare entrambe le tipologie di memorie per provare quale delle due tipologie fosse più sensibile

all'interazione con i single event effect, spiegati nel capitolo 1, ed essere coperti nel caso di malfunzionamento di una delle due, dato che entrambe dovranno principalmente svolgere lo stesso compito.

La memoria doveva essere di dimensioni sufficienti almeno da contenere l'intero fotogramma acquisito, di circa 830Kbyte, quindi la memoria doveva essere almeno da 1Mbyte.

Allora per essere sicuri di avere lo spazio necessario per l'acquisizione e il processamento dell'immagine e per utilizzare anche i restanti due banchi di indirizzamento interno del DSP per memorie asincrone, da 1Mbyte ciascuno, si è deciso di adottare come memoria SRAM, una memoria da 2Mbyte prodotta dalla Toshiba, denominata TC55VBM416AFTN55, prodotta in un package da 48 pin TSOP. La scelta della memoria SRAM di questo produttore è stata forzata dalla scarsa possibilità di scelta di questo tipo di memorie nei cataloghi dei più grandi distributori di componenti elettronici. Infatti il progetto prevedeva l'utilizzo di una memoria simile prodotta da Samsung, ma non reperibile in tempi brevi e mediante canali diretti col Politecnico di Torino; quindi si è utilizzato la memoria della Toshiba, in quanto disponibile presso il distributore Digi-Key e con consumi e tempistiche praticamente identici alla memoria prevista in precedenza.

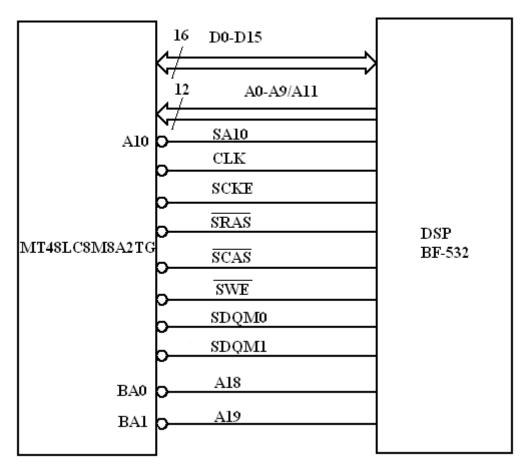

La memoria SDRAM è molto più diffusa e utilizzata nei sistemi embedded, quindi anche più facilmente reperibile presso i distributori. Purtroppo però, solitamente le dimensioni di queste memorie sono molto maggiori di quelle da noi richieste ed inoltre il controller del DSP per memorie esterne sincrone supportava un indirizzamento da 16Mbyte a 128Mbyte. Il problema fondamentale è che una memoria sincrona deve eseguire il refresh di tutte le righe ogni qualche decina di millisecondi e quindi, maggiori sono le dimensioni della memoria, maggiore è il numero di righe, maggiore è la corrente assorbita e quindi maggiori consumi energetici. Quindi bisognava cercare di adottare una memoria di ridotte dimensioni e adatta alle nostre necessità di avere almeno 2Mbyte di indirizzamento del DSP contigui, per poter indirizzare il fotogramma acquisito e altri possibili stream di dati necessari per il processamento dell'immagine.

Si è deciso quindi di utilizzare una memoria di dimensioni di 8Mbyte, la quale appunto garantiva di avere 4 locazioni di memoria contigue da 2Mbyte ciascuna, come verrà spiegato meglio in seguito; essa è prodotta da Micron, denominata MT48LC4M16A2TG, disponibile in un package standard di tipo TSOP a 54 pin.

## 2.3 Funzionamento componenti principali

#### 2.3.1 DSP Blackfin BF-532

Il DSP Blackfin BF-532 di Analog Devices è un processore ad alte performances e bassi consumi, grazie alla possibilità di arrivare ad una frequenza di clock di 400 MHz e varie modalità di funzionamento per una dinamica gestione della potenza assorbita. Infatti la possibilità di variare sia la tensione del core che la sua frequenza, permette di ottimizzare il consumo di potenza per ogni specifico task da eseguire.

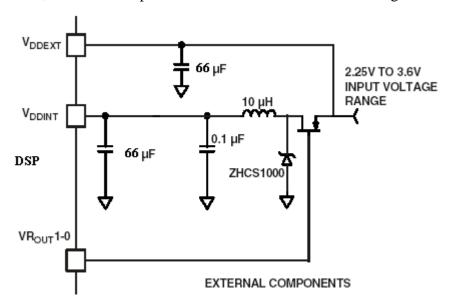

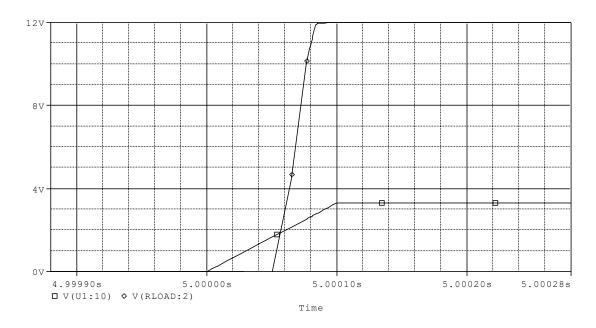

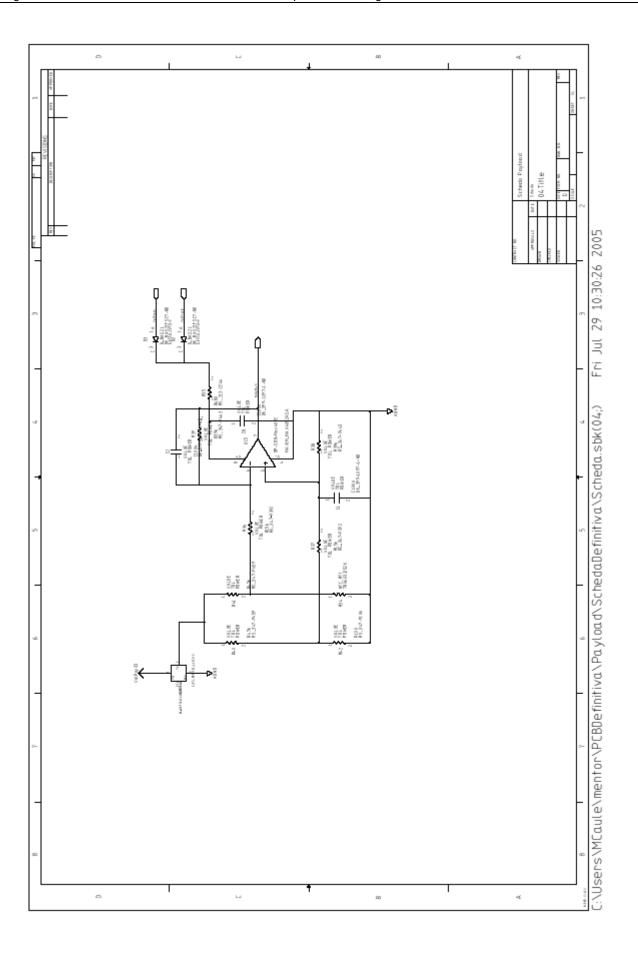

Il processore è alimentato esternamente a 3,3V, ma tale tensione è utilizzata per alimentare tutte le periferiche, mentre l'alimentazione del core è ottenuta mediante un regolatore di tensione interno che comanda un regolatore di tensione switching di tipo buck, montato a componenti discreti esternamente sulla scheda Payload. Il regolatore da una tesnisone d'ingresso da 2,25V a 3,6V, fornisce da 0,8V a 1,2V al core del processore. Lo schema utilizzato è il seguente:

Figura 2.5: Circuito del regolatore di tensione

Il transistor disponibile in forma di circuito integrato su 3 pin in package SOT-23, è prodotto dall'International Rectifier e presenta una tensione di soglia  $V_{GS}$  massima di -0.95V, che quindi lo rende pilotabile dal comando a 3.3V dato dai due pin.

Inoltre è stato utilizzato un diodo shottcky ZHCS1000 da 1A, disponibile anch'esso in un package a 3 pin SOT-23 e un induttore da 10µH, anch'esso da 1A e disponibile in package smd chiamato SLF 7mm x 7mm x 3,2mm, prodotto da TDK.

Due pin (cortocircuitati) del processore, chiamati VROUT0 e VROUT1, forniscono il segnale a onda quadra ad una frequenza di circa 300 kHz al gate del P-MOS discreto per ottenere la tensione destinata al core del processore.

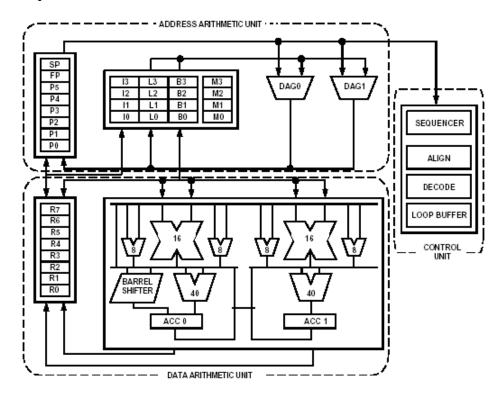

Il core del Blackfin BF-532 ha una struttura interna costituita da sei unità funzionali principali per l'esecuzione di algoritmi sia di processamento numerico che di controllo generico dei segnali provenienti dall'esterno; il DSP presenta:

- due unità MAC (Multiply Accmulate) da 16 bit

- due unità aritmetico/logiche (ALU) da 40 bit

- uno shifter di tipo Barrell

- un set di quattro ALU Video

Figura 2.6: Architettura del core del processore

Le due unità MAC vengono utilizzate per operazioni di moltiplicazione o moltiplicazione e accumulo con addizione o sottrazione. Infatti i moltiplicatori operano su dati a virgola fissa a 16 bit e producono quindi risultati a 32 bit i quali possono essere sommati o sottratti dal registro accumulatore a 40 bit.

Il software che poi verrà eseguito per la compressione dell'immagine in formato JPEG utilizzerà pesantemente tali unità funzionali, rendendo la compressione molto più veloce rispetto ad un processore general purpose.

Le due unità ALU, sono ovviamente utilizzate dalle operazioni seguenti, presenti nel codice poi sviluppato, per compiere le varie funzione richieste dalle specifiche:

- somme e sottrazioni di registri in virgola fissa

- accumulo e sottrazione di risultati dei moltiplicatori

- funzioni logiche AND, OR, NOT, XOR

- funzioni: ABS, MAX, MIN

Il barrell shifter è ovviamente utilizzato per le operazioni di shift aritmetico e logico dei bit su registri da 16, 32 e 40 bit, rotazioni e vari test sui bit.

Infine, il set di quattro ALU vengono utilizzate per il processamento dei segnali video con alta efficienza; ogni ALU video prevede come input da una a quattro coppie di registri a 8 bit e come output da uno a quattro registri da 8 bit; tra le funzioni implementate vi sono somma e sottrazioni, medie, packing o unpacking dei dati.

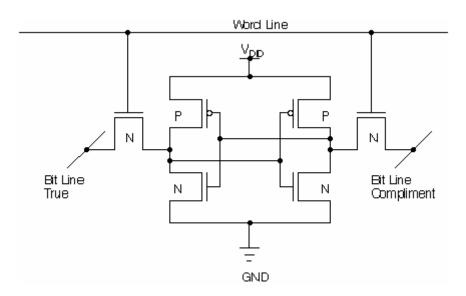

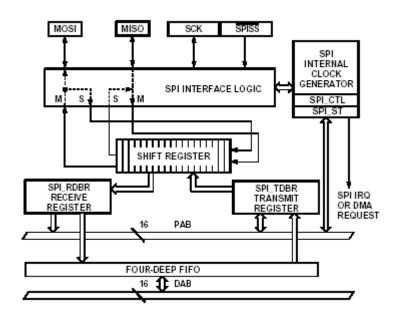

La funzione utilizzata da quelle offerte delle ALU Video dal software della scheda Payload è quella di packing dei dati. Infatti i dati video acquisiti nel formato ITU-R BT.656-4 sono a 8 bit e sono destinati a essere salvati su una memoria esterna SRAM o SDRAM. Entrambe prevedono un parallelismo dei dati, data bus, di 16 bit. Quindi questa funzione permette di accedere alla memoria esterna alla metà della frequenza con cui sono acquisiti i dati, sfruttando pienamente ogni cella di memoria e rendendone meno stringenti le tempistiche. Infatti così il DMA controller può acquisisce due dati a 8 bit dalla porta video a 27 MHz ( che corrisponde a un periodo di 37 ns), li "impacca", ossia li mette insieme in unico dato a 16 bit mediante un'ALU Video e poi li va salvare nella memoria destinazione, ad una frequenza di 13,5Mhz (ossia 74 ns).

Infine il DMA verrà settato in modalità di acquisizione di un singolo fotogramma, chiamato DMA STOP Mode, e qundi alla fine di questo il controller si fermerà generando un interrupt; infatti il processore prevede anche una modalità di acquisizione continua, utile per i video.

L'architettura della memoria interna del processore Blackfin è costituita da tre blocchi, i quali consentono un accesso ad elevata velocità dal core del processore; i tre blocchi sono i seguenti:

- L1 memoria codice, che consiste in una SRAM e/o una 4-way set associative cache. La velocità di accesso di questa memoria è la stessa del core. La memoria è costituita da due blocchi, una solo come SRAM da 32 Kbyte e una utilizzabile sia come SRAM e come cache da 16 Kbyte.

- L1 memoria dati da 32 Kbyte, che consiste in una SRAM e o un 2-way set associative cache. Anche questa memoria è utilizzata alla piena velocità del core.

- L1 scratchpad RAM di 4 Kbyte, la quale permette la stesa velocità di accesso delle altre due ma non può essere utilizzata come memoria cache ma solo com SRAM dati.

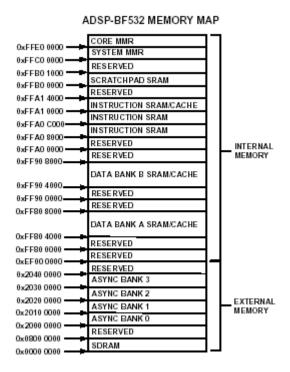

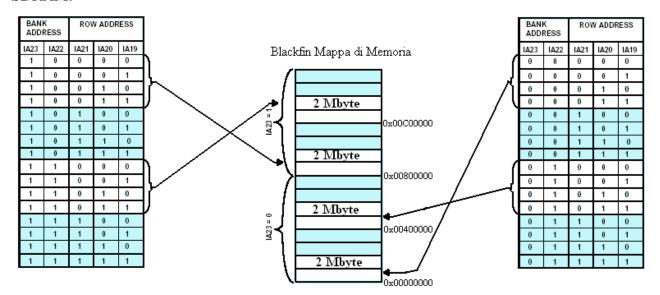

Nel nostro sistema il software si prevede che abbia dimensioni massime di circa 200 Kbyte, quindi i 48 Kbyte di memoria codice interna non sono sufficienti (senza utilizzarla come cache), quindi a seconda della modalità di boot predefinità, il codice verrà mantenuto su una memoria esterna tipo SDRAM o FLASH, come verrà spiegato in seguito. La seguente tabella riporta la mappa di memoria intera del processore e spiega in modo migliore la sua struttura, fornendo anche gli indirizzi utilizzati per accedere alle varie aree di memoria:

Figura 2.7: Mappa di memoria Blackfin BF-532

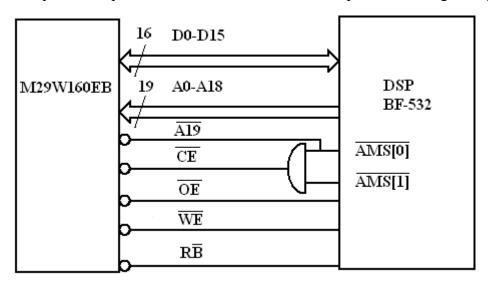

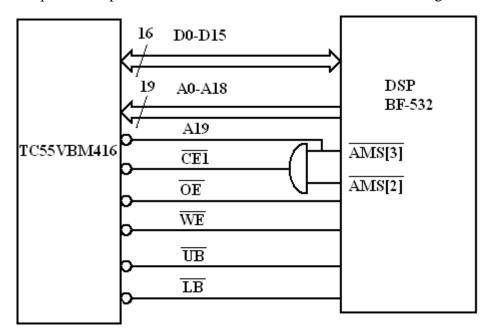

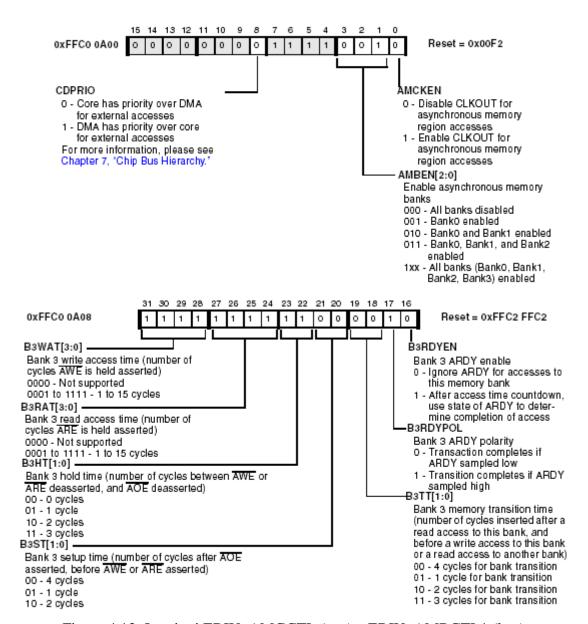

La memoria esterna è gestita tramite l'External Bus Interface Unit (EBIU). Esso è suddiviso in due controller, uno per memorie sincrone SDRAM fino al tipo PC133 e uno per memorie asincrone quali FLASH, SRAM, EEPROM, ROM, etc. Quest'ultimo viene chiamato Asynchronous Memory Interface e permette l'accesso di quattro banchi di memoria esterna, denominati ASYNC BANK come si può vedere dalla figura 2.7, ciascuno di dimensioni di 1Mbyte. Quindi in totale può gestire 4Mbyte di memoria asincrona esterna. Come spiegato in precedenza, il sistema Payload prevede l'utilizzo di una memoria FLASH di 2Mbyte per contenere il programma da eseguire all'avvio e le cinque possibili foto scattate dalle videocamere, da trasmettere poi a terra, e l'utilizzo di una memoria SRAM come memoria temporanea per il fotogramma acquisito dalla porta video, in alternativa all'utilizzo della memoria SDRAM. Quindi tutti e 4Mbyte gestibili dall'interfaccia per memorie asincrone è utilizzato. Qui di seguito viene riportata la tabella d'indirizzamento dei quattro banchi, dove i segnali AMS sono gli Asynchronous Memory Select di ogni banco utilizzato e quindi i chip select per ciascuna memoria gestita dal banco:

| Memory Bank Select | Address Start | Address End |

|--------------------|---------------|-------------|

| AMS[3]             | 2030 0000     | 203F FFFF   |

| AMS[2]             | 2020 0000     | 202F FFFF   |

| AMS[1]             | 2010 0000     | 201F FFFF   |

| AMS[0]             | 2000 0000     | 200F FFFF   |

Figura 2.8: Range indirizzamento Banchi di memoria asincrona

Il controller SDRAM permette di gestire memorie di questo tipo dalle dimensioni di 16 Mbyte a 128 Mbyte massimo, alla velocità massima delle memorie PC133, cioè 133 MHz di clock. Il controller permette inoltre di usare al massimo quattro banchi di memoria esterna distinti, quindi prevede anche una codifica del banco da utilizzare, fatta sui bit d'indirizzo 18 e 19, mentre i primi 15 bit sono disponibili per essere utilizzati come address bus. Inoltre è previsto la possibilità di mascherare gli 8 bit più significativi o quelli meno significativi, tramite due segnali, chiamati SDQM[0] e SDQM[1], mentre se sono posti entrambi a '0', viene letta l'intera word sui 16 bit del data bus.

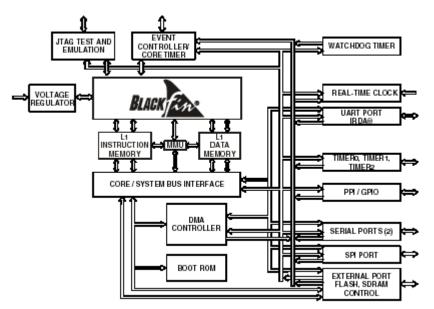

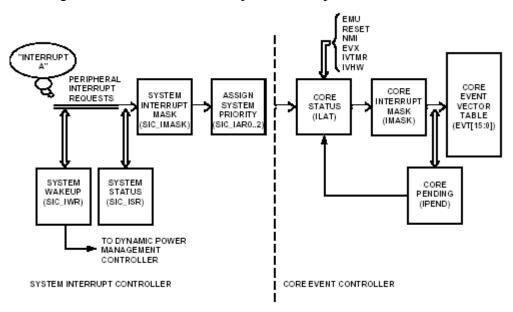

Le periferiche sono connesse al core medianti molti bus ad alta banda, come si può vedere dalla figura seguente:

Figura 2.9: schema a blocchi processore

Oltre all'External Bus Interface Unit, il sistema di periferiche include diverse interface e unià funzionali:

• Parallel Port Interface (PPI)

- Serial Ports (SPORTs)

- Serial Perpheral Interface (SPI)

- Universal Asynchronous Receiver Transmitter(UART)

- General-purpose timers

- Real time clock timer

- Watchdog timer

- General pur pose I/O

Nel sistema Payload, i diversi tipi di timers non sono utilizzati. Inoltre anche le porte seriali generiche, denominate SPORTS, presenti in due unità, non sono direttamente utilizzate; infatti, dato che i canali di comunicazione con i due processori che gestiscono il sistema PICPOT, ProcA e ProcB, saranno rispettivamente le due porte seriali standard UART e SPI, come richiesto da specifiche, allora le SPORTs sono state collegate in parallelo, una al canale UART e una al SPI, in modo tale che se una delle due porte non avesse funzionato, le sarebbe stato implementato un driver SPI-like o UART-like per poter comunicare con i due processori.

La porta denominata PPI è la porta parallela a 8 bit più un segnale di clock compatibile col formato video digitale ITU-R BT.656-4, che verrà collegata al decoder video per l'acquisizione del fotogramma dalle videocamere.

Infine i general-purpose I/O è costituito da 16 pin, i quali però sono multiplexati con alcuni segnali della porta PPI, dei timer e dei slave select SPI. Nel sistema Payload, di questi 16 pin se ne sono utilizzati 4 per la PPI (PPI4, PPI5, PPI6, PPI7) e uno per il segnale di slave select input della porta SPI, chiamato SPISS (SPI Slave Select). Quindi i restanti 11 pin sono stati utilizzati come pin di controllo sulla scheda Payload.

Questi pin possono essere configurati come sensibili al fronte o al livello logico, la polarità del fronte o del livello che li rende attivi e la loro direzione ossia, se viene utilizzato come pin d'ingresso (valore di default) o come pin d'uscita. Qui di seguito viene riportata la tabella riassuntiva di come sono stati impiegati questi general purpose pin:

| DISPOSITIVO | PIN | NOME | FUNZIONE |

|-------------|-----|------|----------|

|             | 33  | PF11 | SDA      |

| DECODER PAL | 34  | PF10 | SCL      |

|             | 35  | PF9  | HSYNC    |

|             | 36  | PF8  | RESET    |

|             | 38  | PF6  | AVID     |

|                | 49 | PF2 | VSYNC            |

|----------------|----|-----|------------------|

|                | 50 | PF1 | FID/GCLO         |

|                | 37 | PF7 | INTREQ/GPCL/VBLK |

| SWITCH TELECAM | 46 | PF5 | TELECAM1         |

|                | 47 | PF4 | TELECAM2         |

|                | 48 | PF3 | TELECAM3         |

Figura 2.10: descrizione connessioni general purpose I/O pin

La maggior parte sono stati utilizzati per l'interfaccia col decoder video, mentre i restanti tre sono stati impiegati per la gestione dei load switch, spiegati in precedenza per l'alimentazione delle videocamere.

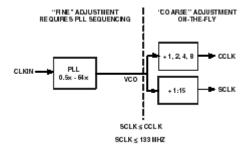

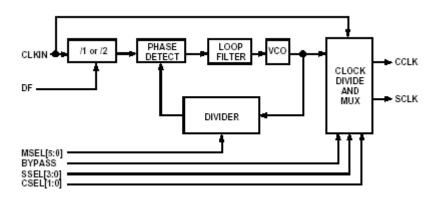

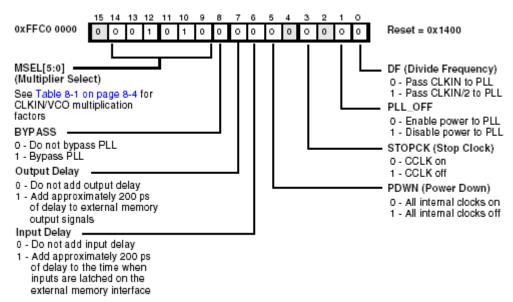

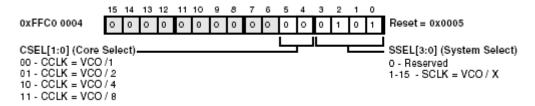

Come è stato accennato all'inizio di qusto paragrafo, la frequenza del core e delle periferiche è ottenuta tramite un quarzo esterno e poi agganciata ad un PLL frazionario, che quindi utilizza un divisore programmabile per ottenere una frequenza massima di 400 MHz. Inoltre i segnali di clock, ossia quelli uscenti dal VCO, destinati alle periferiche (chiamato SCLK) e al core (chiamato CCLK) sono distinti, e sui due sono presenti due divisori distinti, in modo da avere la possibilità di avere le periferiche a bassa frequenza ma il core ad una più elevata; questo comporta un notevole risparmio di potenza, dato che le periferiche sono alimentate a 3,3V. Lo schema è il seguente:

Figura 2.11: catena di gestione del clock

Il quarzo utilizzato per il processore BF-532 è da 11.0592 MHz, prodotto dalla FOX Electronics in package smd denominato HC49SD. Il divisore del PLL è stato settato a 36x, in modo tale da avere un VCO a 398.1312 MHz. Così si è poi settato i due divisori a 4, così da avere le due frequenze sulle periferiche e sul core uguali a 99.5328 MHz. Questo permette di utilizzare la memoria SDRAM adottata in modalità PC100 e di non consumare eccessivamente col core.

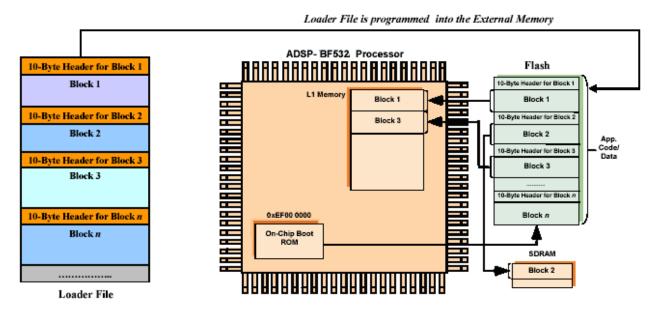

Interessante particolarità del processore Blackfin è la modalità di boot; esso prevede tre modalità di boot diverse, due delle quali caricano internamente il programma da una memoria esterna nella memoria codice interna L1, dopo aver ricevuto il comando di reset esterno. Un terzo modo prevede, sempre dopo il reset, l'esecuzione del programma direttamente dalla memoria esterna, saltando la

sequenza di boot. La modalità di boot viene impostata esternamente mediante due pin, chiamati BMODE0 e BMODE1, del processore; un piccolo boot kernel presente all'interno della Boot ROM interna del processore, campiona dopo il reset il valore dei due pin e agisce secondo la seguente tabella:

| Boot Source                                                                                                  | BMODE[1:0] | Execution Start<br>Address |

|--------------------------------------------------------------------------------------------------------------|------------|----------------------------|

| Bypass boot ROM; execute from 16-bit wide exter-<br>nal memory (Async Bank 0)                                | 00         | 0x2000 0000                |

| Use boot ROM to boot from 8-bit or 16-bit flash                                                              | 01         | 0xEF00 0000                |

| Reserved                                                                                                     | 10         | 0xEF00 0000                |

| Use boot ROM to configure and load boot code<br>from SPI serial EEPROM (8-, 16-, or 24-bit address<br>range) | 11         | 0xEF00 0000                |

Figura 2.12: Modalità di boot

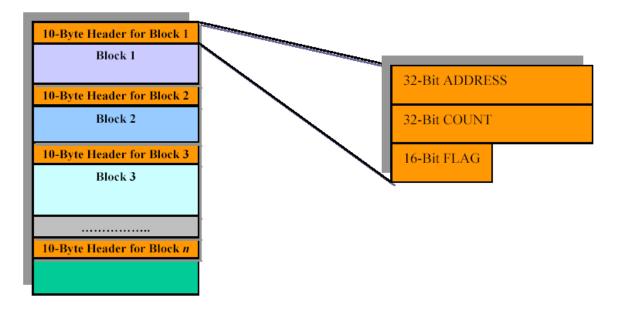

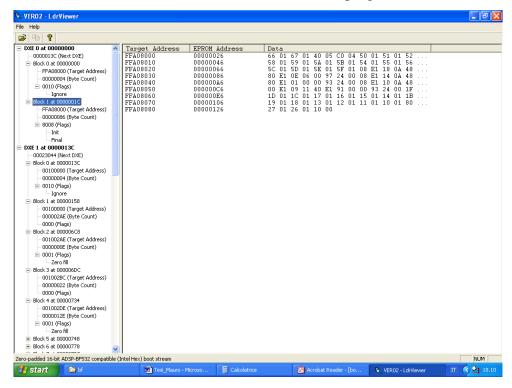

Per ogni modalità di boot, un header di 10 byte è dapprima letto dalla memoria esterna; esso specifica il numero di byte trasferiti e l'indirizzo della memoria destinazione; appena tutti byte sono stati caricati, l'esecuzione inizia dall'indirizzo iniziale della memoria codice L1, 0xFFA08000, come si può vedere in figura 2.7.

Nel sistema Payload le modalità di boot utilizzate sono le prime due, codificate con 00 e 01. Infatti il programma è contenuto nella memoria esterna FLASH a 16-bit. In queste due modalità, il processore esegue il boot dall'indirizzo iniziale del banco 0 delle memorie asincrone, ASYNC Bank 0 all'indirizzo 0x2000000. Ecco che quindi la memoria FLASH sarà utilizzata mediante i primi due banchi, banco 0 e banco 1, dell'Asynchronous Memory Interface, mentre qundi i restanti due banchi saranno utilizzati per indirizzare i dati sulla memoria SRAM esterna.

La differenza delle due modalità di boot è che quella codificata 00 viene eseguita direttamente sulla memoria FLASH esterna, mentre nell'altra modalità, codificata 01, il processore punta alla Boot Rom la quale scarica tutto il programma in L1, riempiendola, e la restante parte in SDRAM esterna, dato che il programma sarà di circa 200 Kbyte e la L1 solo di 48 Kbyte in totale. Come verrà realizzato ciò, sarà spiegato in seguito nel capitolo dedicato al Software.

Le modalità di boot che vengono quindi impiegate, prevedono sempre uno dei due bit a zero, BMODE1, il quale è stato quindi collegato a massa.

L'altro pin, BMODE0, può assumere sia '1' che '0' a seconda della modalità di boot selezionata. La selezione avverrà da parte del processore che ha richiesto il funzionamento della scheda Payload, dando quindi la possibilità di pilotare tale pin da parte del ProcA o del ProcB. Tale possibilità è

stata garantita collegando i due segnali digitali provenienti dai processori ad una porta logica AND, collegata in uscita al pin di boot del processore. Il gate è quello sotto forma integrata utilizzato dalle memorie due memorie asincrone, come verrà spiegato in seguito, è prodotto dalla Texas Instruments denominato SN74AGC1G08. Dato che questa soluzione no è stata pienamente testata in fase di prototipazione, sui due segnali provenienti da i processori ProcA e ProcB, è stata posta una resistenza serie da  $0\Omega$ , per garantire la possibilità di scollegare il segnale in caso di funzionamento errato, e la possibilità di collegare una resistenza di pull-up da  $10k\Omega$  e pull-down da  $0\Omega$ . Inoltre queste ultime due sono state previste anche all'uscita del gate AND.

L'assorbimento di corrente da parte del gate AND integrato è di circa 10  $\mu A$ , comportando un consumo di potenza di circa 33  $\mu W$ .

Il processore Blackfin esegue il boot dopo aver ricevuto un segnale di reset da un pin esterno di durata minima di 11 cicli di clock esterno; la scheda Payload adotta un quarzo da 11.0592 MHz, corrispondente a 90,42 ns, quindi la durata del segnale di reset deve essere di almeno 994,64 ns, ossia 1 µs.

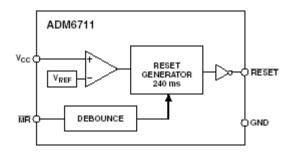

Nel sistema Payload il boot deve avvenire ad ogni accensione della scheda e quindi si adottato un circuito integrato di power-on reset, esterno al Blackfin, il quale per almeno 140 ms dall'accensione del sistema, tiene a livello logico basso il pin di reset del processore. Lo schema a blocchi del componente integrato è il seguente:

Figura 2.13: Schema a blocchi ADM6711

Come si vede dalla figura precedente, l'ADM6711 prodotto da Analog Devices e disponibile in package di dimensioni molto compatte SC70, prevede anche la possibilità di collegare un pulsante esterno, che mediante un circuito anti-rimbalzo genererebbe un reset asincrono; questo non è stato utilizzato sulla scheda definitiva ma solo sul prototipo, dato che quando la scheda sarà installata all'interno del satellite nessuno potrà comandare il pulsante.

Dallo schema a blocchi si capisce che il componente attende 140 ms da quando l'alimentazione ha sorpassato una certa soglia; per il sistema Payload la soglia adottata è di 2,95V, garantiti costanti fino a circa 85°C, con un buon margine di sicurezza sui 3,3V forniti dalla scheda PowerSwitch.

L'assorbimento in termini di corrente da parte della circuiteria interna è di circa  $12~\mu A$ , comportando un consumo di potenza di circa  $40~\mu W$ .

Il consumo di corrente e di potenza del processore Blackfin risulta piuttosto complesso da calcolare; infatti, esso sarà composto dal consumo del core, sommato al consumo di tutti i componenti esterni attivi, ossia in commutazione:

$$P_{TOTAL} = P_{EXT} + (I_{DD} \times V_{DDINT})$$

l'assorbimento dei componenti esterni infatti, dipende dal numero di pin coinvolti (0), dalla frequenza di commutazione (dei pin coinvolti, quindi la metà del clock utilizzato nei protocolli sincroni quali quello SDRAM, ITU-R BT.656-4 e SPI, in quanto transizioni successive '0'-'1' e '1'-'0' su linee dati o indirizzi avvengono ogni due cicli di clock), il cui valore non può superare quello del clock del processore per le periferiche (SCLK), dalla tensione di funzionamento, tipicamente 3,3V e dalla capacità d'ingresso (C), delle porte CMOS dei componenti integrati:

$$P_{EXT} = O \times C \times V_{DD}^2 \times f$$

In seguito verranno presentati il funzionamento dei vari componenti presenti sulla scheda Payload e la loro interfaccia con il processore; per ognuno quindi verrà calcolato il loro consumo interno e dell'interfaccia, in modo da poi riassumere i consumi totali del sistema nelle varie fasi di funzionamento nel sottocapitolo CONSUMI ENRGETICI, sapendo che l'assorbimento di corrente del core del processore funzionando a 100 MHz circ è di 60 mA alla tensione di 1,2V nominali.

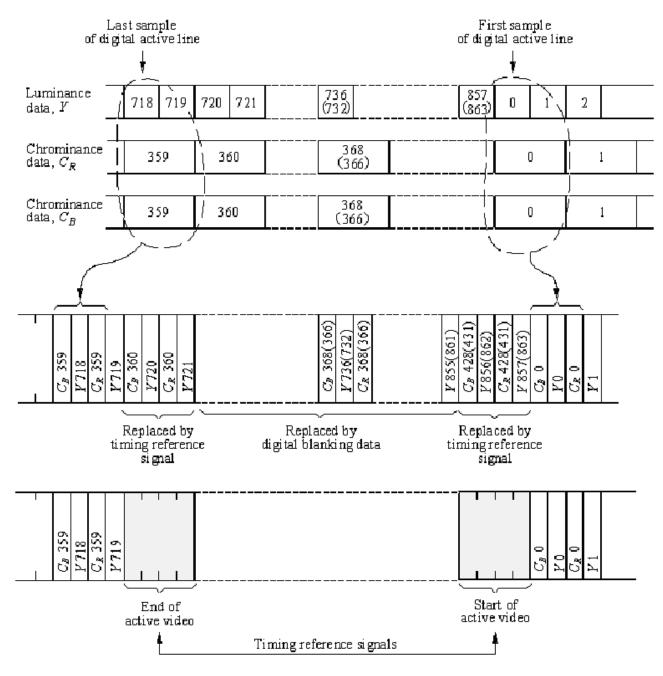

## 2.3.2 Decoder Video TVP5150AP

Il TVP5150AP è un decoder video PAL ultra low power. Disponibile in package molto compatto da 32 pin TQFP, esso converte il segnale PAL ricevuto dalle videocamere nel formato 8 bit ITU-R BT.656-4, in diverse modalità.

L'architettura ottimizata del decoder permette un grande risparmio di potenza assorbita. Infatti il decoder, prevede una modalità di power down, utilizzata dal sistema Payload, quando non vengono utilizzate le videocamere; questo avviene tenendo a livello logico basso il pin chiamato PDN, attivo basso. Inoltre questo componente prevede due tensioni distinte per il core e per le periferiche; infatti queste ultime sono alimentate a 3,3V, mentre il core verrà alimentato a 1,8V; tale tensione sarà ottenuta dalla linea di alimentazione principale a 3,3V mediante un regolatore di tensione low voltage drop out (LDO) esterno, prodotto da Texas Instruments denominato TPS76918, disponibile in package estremamente compatto SOT-23 a 5 pin. Sebbene dalle specifiche del decoder, il consumo di corrente del core dovrebbe essere di circa 55 mA, il regolatore che è stato utilizzato è

in grado di fornire 100 mA, così da non essere molto stressato e quindi non scaldare troppo, in quanto come spiegato in precedenza, il fattore di assenza di atmosfera comporta una notevole difficoltà dei componenti nel dissipare il calore generato.

Il decoder utilizza un quarzo esterno ad una frequenza standard tra i componenti integrati per segnali video, 14.31818MHz prodotto da FOX Electronics e disponibile nel package smd HC49SD. Il decoder contiene diversi registri interni di configurazione sia di caratteristiche video tipo luminosità, contrasto, saturazione, sia di funzionamento delle interfacce. Tali registri di configurazione sono accessibili mediante una porta hardware standard I<sup>2</sup>C; per poter configurare quindi il decoder è stato implementato sul processore BF-532 il protocollo I<sup>2</sup>C via software, il quale per funzionare utilizza due pin general purpose, si veda figura 2.10, il cui funzionamento verrà spiegato in seguito.

La seguente tabella riporta le varie modalità di funzionamento del decoder:

| PDN | RESETB | CONFIGURATION            |

|-----|--------|--------------------------|

| 0   | 0      | Reserved (unknown state) |

| 0   | 1      | Powers down the decoder  |

| 1   | 0      | Resets the decoder       |

| 1   | 1      | Normal operation         |

Figura 2.14: Modalità di Reset e Power Down

Dato che il decoder video viene solo utilizzato nella fase di acquisizione del fotogramma dalle videocamere, si è cercato una soluzione che mantenesse sempre in stand-by il dispositivo durante le altre fasi e fosse attivo in contemporanea a quando una delle videocamere fosse stata accesa. Quindi si è posta una porta OR a 3 ingressi discreta, prodotta da Texas Instruments, chiamata SN74LVC1G332, disponibile in un package ultra compatto SC70, low power in quanto la corrente massima assorbita è di  $10~\mu A$  e quindi  $33~\mu W$  in potenza. Tale dispositivo prende in ingresso i tre segnali (attivi a livello logico alto) che comandano i tre load switch che danno l'alimentazione di 12V ad una delle tre videocamere da cui deve essere acquisito il fotogramma, e l'uscita va a comandare il pin PDN (Power Down) del decoder (attivo basso).

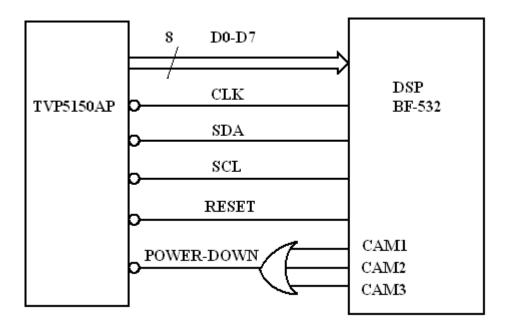

L'interfaccia principale tra il processore e il decoder video è la seguente:

Figura 2.15: Interfaccia PPI, I<sup>2</sup>C e controllo tra decoder video e Blackfin

Quindi appena il processore entra nella fase di acquisizione, accende una delle tre videocamere e, contemporaneamente accende il decoder. Inoltre il processore porterà il pin collegato al reset del decoder video al livello '0', così da far passare il componente dalla configurazione di power down mode a quella di reset, come si può vedere dalla figura 2.13. Infine quindi il processore dopo qualche millisecondo, riempito da altre istruzioni indipendenti come si vedrà nel capitolo successivo del progetto Software, porterà il pin di reset a livello alto e porterà il decoder in modalità di normale operatività.

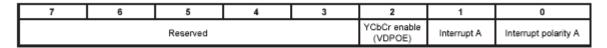

Mediante i registri di configurazione, dopo la routine di accensione descritta in precedenza, vengono settati i due parametri di funzionamento:

- Abilitazione di un'interrupt hardware generato dal decoder su un pin chiamato INTREQ al momento in cui il PLL d'ingresso risulta agganciato al segnale PAL analogico d'ingresso, proveniente da una delle videocamere. Tale pin sarà poi collegato ad un general purpose pin del processore, si veda la figura 2.10, il quale abiliterà immediatamente l'inizio della procedura di acquisizione dell'immagine.

- Abilitazione dei segnali di uscita della porta video, dato che di default si trovano in alta impedenza.

Il decoder video come detto in precedenza permette diverse modalità di acquisizione del formato video. Infatti il segnale video digitale standard, come verrà spiegato in seguito, prevede alcuni segnali di sincronizzazione, relativi alle coordinate orizzontale e verticale del fotogramma acquisito. Tale decoder fornisce uno stream di dati video con incluse queste sincronizzazioni che inoltre

fornisce anche su alcuni pin esterni; essi, come si può vedere dalla figura 2.10, sono stati collegati ad alcuni pin general purpose del processore, per poterne usufruire in caso di malfunzionamenti, in quanto il processore sarà impostato per acquisire solo il segnale video con tutte le sincronizzazioni. Infine, per un corretto funzionamento del componente, è stato messo a massa il secondo canale video, in quanto non utilizzato, mediante un condensatore da 100 nF.

Il consumo di corrente del decoder è diverso nelle due modalità di funzionamento:

## Normal mode:

| Alimentazione | Corrente | Potenza  |  |  |

|---------------|----------|----------|--|--|

| 3.3V I/O      | 4.8 mA   | 15.84 mW |  |  |

| 1.8V core     | 55.1 mA  | 99.18 mW |  |  |

Nel funzionamento normale quindi l'assorbimento normale dovrebbe essere di 115 mW. Dal datasheet del componente si deve tenere come valore conservativo di potenza massima assorbita 150 mW.